# Power Ballast and Dual LED Driver for Automotive Front Lighting

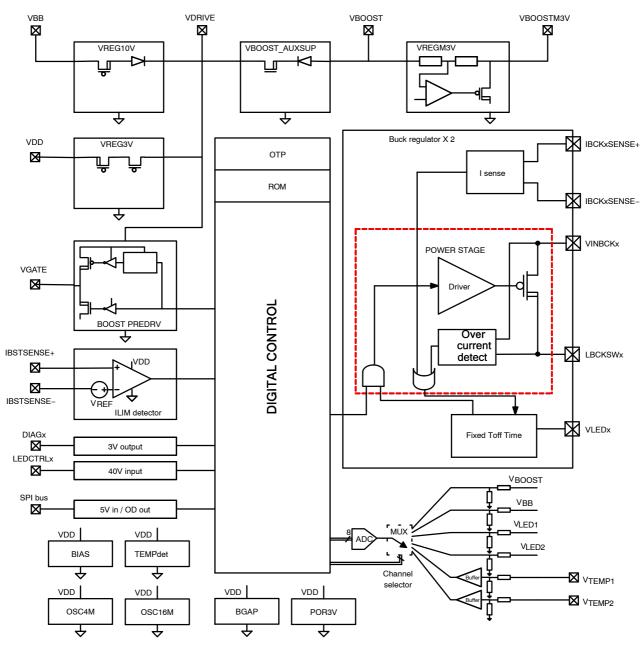

The NCV78663 is a single-chip and high efficient smart Power ballast and Dual LED DRIVER designed for automotive front lighting applications like high beam, low beam, daytime running light (DRL), turn indicator, fog light, static cornering, and so on.

The NCV78663 is a best fit for high current LEDs and provides a complete solution to drive two strings up to 60 V, by means of two internal independent buck switch channels, with a minimum of external components.

For each channel, the output current and voltage can be customized according to the application requirements. Diagnostic feature for automotive front lighting is provided on-chip.

The device integrates a voltage booster controller, realizing a unique input current filter with a limited number of externals.

The NCV78663 can be used in stand-alone mode or together with a companion microcontroller allowing maximum flexibility. Depending on the voltage and current of the connected LED string, the LED ballast parameters can be adapted by writing the SPI settings in the device, as such that no hardware changes are required.

#### Features

- Single Chip Boost–Buck Solution

- Two Independent LED Strings Up to 60 V

- High Overall Efficiency

- Minimum of External Components

- Active Input Filter with Low Current Ripple from Battery

- Integrated Switched Mode Buck Current Regulator

- Two Integrated Buck Switches with 1.4 A Peak Current Capability

- Integrated Boost Controller

- Programmable Input Current Limitation

- Average Current Regulation Through the LEDs

- High Operating Switching Frequencies to Reduce Inductor Sizes

- Integrated PWM Dimming with Wide Frequency Range

- Low EMC Emission for LED Switching and Dimming

- SPI Interface for Optional External μC and Dynamic Control of System Parameters

- This is a Pb–Free Device

#### **Typical Applications**

- High Beam

- Low Beam

- DRL

- Position or Park light

- Turn Indicator

- Fog Light

- Static Cornering

# **ON Semiconductor®**

http://onsemi.com

#### **ORDERING INFORMATION**

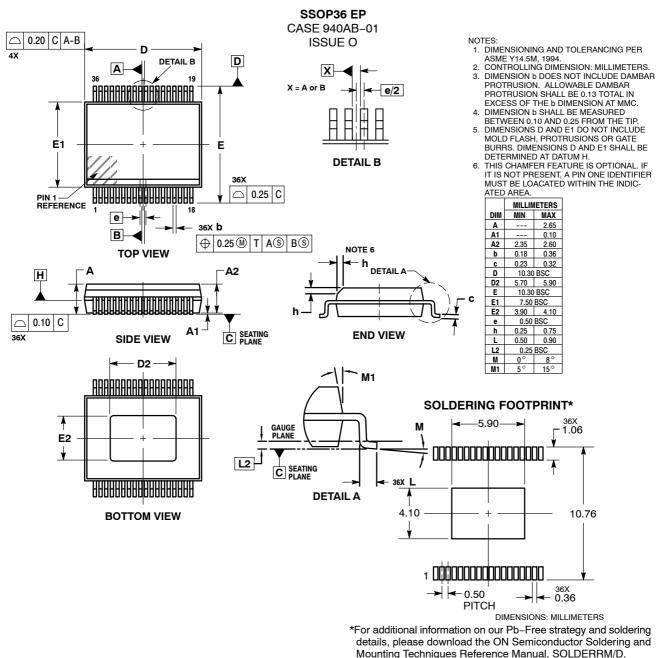

See detailed ordering and shipping information in the package dimensions section on page 36 of this data sheet.

Figure 1. Internal Block Diagram

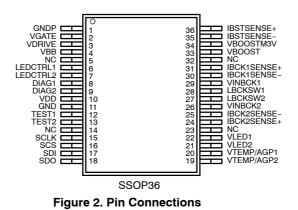

# PACKAGE AND PIN DESCRIPTION

## Table 1. PIN DESCRIPTION

| Pin# | Pin Name    | Ю Туре           | Function                                              |

|------|-------------|------------------|-------------------------------------------------------|

| 1    | GNDP        | ground           | Power ground                                          |

| 2    | VGATE       | MV out           | Booster MOSFET gate pre-driver                        |

| 3    | VDRIVE      | MV supply        | 10 V supply                                           |

| 4    | VBB         | HV supply        | Battery supply                                        |

| 5    | N.C.        |                  | Not used (can be connected to GND)                    |

| 6    | LEDCTRL1    | HV IO            | LED string 1 enable                                   |

| 7    | LEDCTRL2    | HV IO            | LED string 2 enable                                   |

| 8    | DIAG1       | LV out           | LED string 1 diagnostic output                        |

| 9    | DIAG2       | LV out           | LED string 2 diagnostic output                        |

| 10   | VDD         | LV supply        | 3 V logic supply                                      |

| 11   | GND         | Ground           | Ground                                                |

| 12   | TEST1       | LV in            | Test (not used in application, must connected to GND) |

| 13   | TEST2       | LV in            | Test (not used in application, must connected to GND) |

| 14   | N.C.        |                  | Not used (can be connected to GND)                    |

| 15   | SCLK        | MV in            | SPI clock                                             |

| 16   | SCS (CSB)   | MV in            | SPI chip select (chip select bar)                     |

| 17   | SDI         | MV in            | SPI data input                                        |

| 18   | SDO         | MV<br>open-drain | SPI data output                                       |

| 19   | VTEMP/AGP2  | LV in            | LED string 2 temperature feedback input               |

| 20   | VTEMP/AGP1  | LV in            | LED string 1 temperature feedback input               |

| 21   | VLED2       | HV in            | LED string 2 forward voltage input                    |

| 22   | VLED1       | HV in            | LED string 1 forward voltage input                    |

| 23   | N.C.        |                  | Not used (can be connected to GND)                    |

| 24   | IBCK2SENSE+ | HV in            | Buck 2 positive sense input                           |

| 25   | IBCK2SENSE- | HV in            | Buck 2 negative sense input                           |

| 26   | VINBCK2     | HV in            | Buck 2 high voltage supply                            |

| 27   | LBCKSW2     | HV out           | Buck 2 switch output                                  |

| 28   | LBCKSW1     | HV out           | Buck 1 switch output                                  |

#### Table 1. PIN DESCRIPTION

| Pin# | Pin Name    | Ю Туре    | Function                                |

|------|-------------|-----------|-----------------------------------------|

| 29   | VINBCK1     | HV in     | Buck 1 high voltage supply              |

| 30   | IBCK1SENSE- | HV in     | Buck 1 negative sense input             |

| 31   | IBCK1SENSE+ | HV in     | Buck 1 positive sense input             |

| 32   | N.C.        |           | Not used (can be connected to GND)      |

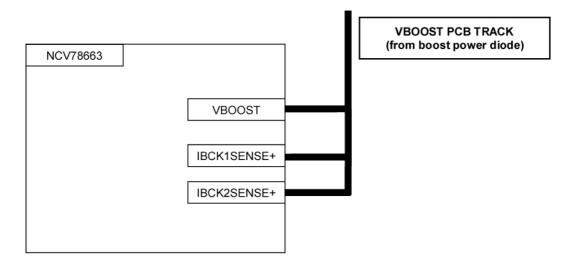

| 33   | VBOOST      | HV supply | High voltage feedback input             |

| 34   | VBOOSTM3V   | HV IO     | VBOOST-3V output                        |

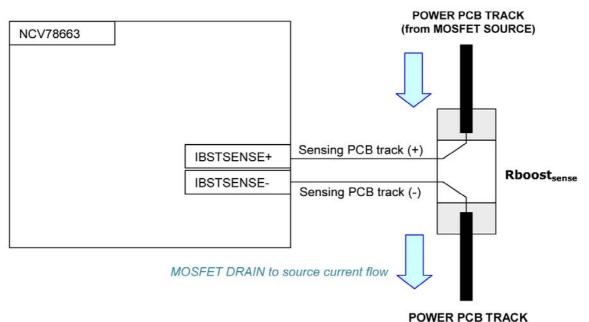

| 35   | IBSTSENSE-  | LV IO     | Battery current negative feedback input |

| 36   | IBSTSENSE+  | LV IO     | Battery current positive feedback input |

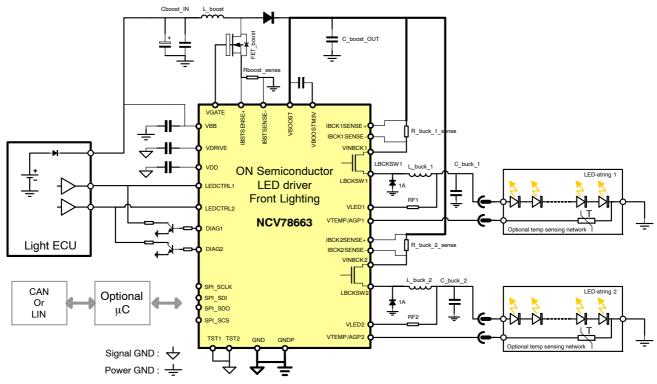

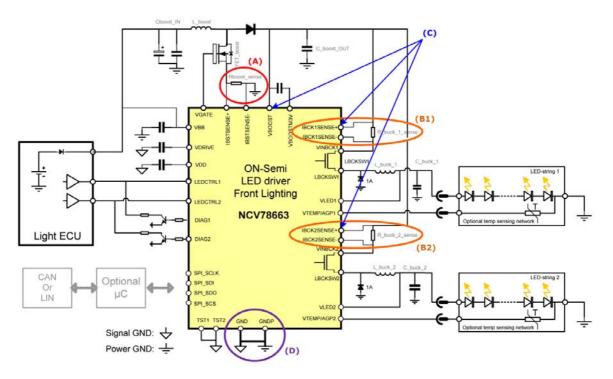

#### Figure 3. NCV78663 Application Circuit

1. As reported in the application diagram, the device pins TEST1 and TEST2 must be connected to ground.

- 2. For details about PCB layout, please refer to the dedicated section.

- 3. RF1 and RF2 resistors typical value is  $2.2 \text{ k}\Omega$  and minimum required value is  $1 \text{ k}\Omega$ . It is recommended not to exceed a value of  $22 \text{ k}\Omega$  in order not to alter the VLED sampled value.

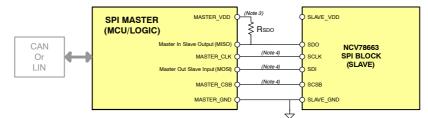

Figure 4. Details on NCV78663 Connection Diagram for SPI (Optional)

- 4. R<sub>SDO</sub> external resistor typical value is 1 kΩ. An additional capacitor to ground (typically 47 pF) may be used in case of application noise observed.

- 5. External capacitors or RC may be added to these SPI lines for stable communication in case of application noise. The selection of these components must be done so that the resulting waveforms are respecting the limits reported in Table 23.

## **OPERATING CONDITIONS**

#### Table 2. ABSOLUTE MAXIMUM RATINGS

| Characteristic                                       | Symbol                    | Min       | Max       | Unit |

|------------------------------------------------------|---------------------------|-----------|-----------|------|

| Battery Supply voltage (Note 6)                      | VBB                       | -0.3      | 60        | V    |

| LED supply voltage (Note 7)                          | VBOOST                    | -0.3      | 68        | V    |

| Logic Supply voltage                                 | VDD                       | -0.3      | 3.6       | V    |

| Low voltage I/O pins (Note 8)                        | IOLV                      | -0.3      | VDD + 0.3 | V    |

| Gate driver supply voltage (Note 9)                  | VDRIVE                    | -0.3      | 12        | V    |

| GNDP voltage                                         | GNDP_V                    | -0.3      | 0.3       | V    |

| Input current sense voltage                          | IBSTSENSE+,<br>IBSTSENSE- | -1.0      | 3.6       | V    |

| Medium voltage IO pins (Note 10)                     | IOMV                      | -0.3      | 7.0       | V    |

| Buck switch low side                                 | LBCKSW1,<br>LBCKSW2       | -2.0      | VBOOST    | V    |

| Relative voltage IO pins (Note 11)                   | ΔV_IO                     | VBOOSTM3V | VBOOST    | V    |

| Storage Temperature                                  | Tstrg                     | -50       | 135       | °C   |

| Buck switch output current (Note 12)                 | I_LBCKSW                  |           | 1.4       | А    |

| Electrostatic discharge on component level (Note 13) | VESD                      | -2        | +2        | kV   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

6. Absolute maximum rating for pins: VBB, LEDCTRL1, LEDCTRL2.

- 7. Absolute maximum rating for pins: VBOOST, VBOOSTM3V, IBCK1SENSE+, IBCK1SENSE-, VINBCK1, VLED1, IBCK2SENSE+, IBCK2SENSE-, VINBCK2, VLED2.

- 8. Absolute maximum rating for pins: TEST1, TEST2, VTEMP1, VTEMP2, DIAG1, DIAG2.

- 9. Absolute maximum rating for pins: VDRIVE, VGATE.

- 10. Absolute maximum rating for pins: SCLK, SCS, SDI, SDO.

- 11. Relative maximum rating for pins: VINBCK1, VINBCK2, IBCK1SENSE+, IBCK2SENSE+, IBCK1SENSE-, IBCK2SENSE-, I

12. Peak value.

13. Human Body Model (100 pF via 1.5 kΩ, according to JEDEC EIA/JESD22-A114).

#### Table 3. RECOMMENDED OPERATING CONDITIONS

Operating ranges define the limits for functional operation and parametric characteristics of the device. Note that the functionality of the device outside the operating ranges described in this section is not warranted. Operating outside the recommended operating ranges for extended time may affect device reliability. A mission profile (Note 14) is a substantial part of the operation conditions, hence the Customer must contact ON Semiconductor in order to mutually agree in writing on the allowed missions profile(s) in the application.

| Characteristic                       | Symbol              | Min | Max | Unit |

|--------------------------------------|---------------------|-----|-----|------|

| Battery Supply Voltage               | VBB                 | 5   | 40  | V    |

| Battery Supply Current (Note 15)     | IBB                 |     | 20  | mA   |

| Logic Supply Output Current          | IDD                 |     | 10  | mA   |

| 5V Tolerant IO pins                  | DIG_IO_V            | 0   | 5.5 | V    |

| VTEMP/AGPx pins                      | VTEMPAGP_V          | 0.3 | VDD | V    |

| Gate Driver Supply Current (Note 16) | Idrive              |     | 10  | mA   |

| Ambient Temperature                  | T <sub>A</sub>      | -40 | 125 | °C   |

| Junction Temperature                 | TJ                  | -45 | 170 | °C   |

| VBB Voltage during OTP Zapping       | V <sub>BB_ZAP</sub> | 13  | 40  | V    |

| OTP zap Ambient Temperature          | T <sub>A</sub> _zap | 10  | 30  | °C   |

| Buck Switch Output Current (Note 17) | I_LBCKSW            |     | 1.2 | А    |

14. A mission profile describes the application specific conditions such as, but not limited to, the cumulative operating conditions over life time, the system power dissipation, the system's environmental conditions, the thermal design of the customer's system, the modes, in which the device is operated by the customer, etc.

$15. \text{VBB} = 13 \text{ V}; \text{ I}_{\text{drive}} = 10 \text{ mA}$

16. VBB = 13 V; I<sub>drive</sub> = Q\_gate x f\_boost

17. Average value

#### Table 4. THERMAL RESISTANCE

| Characteristic                             | Package | Symbol           | Мах  | Unit             |

|--------------------------------------------|---------|------------------|------|------------------|

| Thermal resistance junction to exposed pad | SSOP36  | $\theta_{JCbot}$ | 3.49 | KW <sup>-1</sup> |

# **ELECTRICAL CHARACTERISTICS**

NOTE: Unless differently specified, all device Min & Max parameters boundaries are given for the full supply operating range and the junction temperature (T<sub>J</sub>) range (-40;160) (°C).

#### Table 5. VBB: BATTERY SUPPLY INPUT

| Characteristic                    | Symbol | Conditions                                               | Min | Тур | Max | Unit |

|-----------------------------------|--------|----------------------------------------------------------|-----|-----|-----|------|

| Nominal Operating Supply<br>Range | VBB    |                                                          | 5   |     | 40  | V    |

| Device Current<br>Consumption     | IBB_0  | buck regulators off, gate drive off,<br>outputs unloaded |     | 6   | 10  | mA   |

#### Table 6. VDRIVE: 10 V SUPPLY FOR BOOST FET GATE DRIVE CIRCUIT

| Characteristic                     | Symbol      | Conditions                                                      | Min                                        | Тур  | Max | Unit |

|------------------------------------|-------------|-----------------------------------------------------------------|--------------------------------------------|------|-----|------|

| VDRIVE regulator output<br>voltage | VDRIVE      | V <sub>BB</sub> > 11 V: VDRIVE generated from<br>VREG10V        | 9                                          | 10   | 11  | V    |

|                                    |             | V <sub>BB</sub> < 10 V: VDRIVE generated from<br>VBOOST_AUXSUP* | MAX(<br>5.5;<br>V <sub>BB</sub> –<br>1.65) | 7.8  |     | V    |

| DC output current capability       | lout_VDRIVE |                                                                 |                                            |      | 15  | mA   |

| Output current limitation          | ILIM_VDRIVE | V <sub>BB</sub> > 11 V: VDRIVE generated from<br>VREG10V        | 36                                         |      | 185 | mA   |

|                                    |             | V <sub>BB</sub> < 10 V: VDRIVE generated from<br>VBOOST_AUXSUP  | 15                                         |      | 190 | mA   |

| Typical VDRIVE external            | C_VDRIVE    |                                                                 |                                            | 0.47 |     | μF   |

| decoupling capacitor               | ESR         |                                                                 |                                            |      | 200 | mΩ   |

\*Boost regulator must be active.

#### Table 7. VDD: 3 V LOW VOLTAGE ANALOG DIGITAL SUPPLY

| Characteristic                  | Symbol     | Conditions     | Min  | Тур  | Max  | Unit |

|---------------------------------|------------|----------------|------|------|------|------|

| VDD regulator output voltage    | VDD        | VDRIVE > 4.5 V | 2.9  | 3    | 3.1  | V    |

| DC output current capability    | lout_VDD   | VDRIVE > 4.5 V |      |      | 10   | mA   |

| Output current limitation       | llim_VDD   | VDRIVE > 4.5 V | 40   |      | 200  | mA   |

| Typical VDD external            | C_VDD      |                | 0.22 | 0.47 | 10   | μF   |

| decoupling capacitor            | ESR        |                |      |      | 200  | mΩ   |

| POR Toggle level on VDD rising  | POR3V_H    |                | 1.43 | 2.3  | 2.54 | V    |

| POR Toggle level on VDD falling | POR3V_L    |                | 1.26 | 2.0  | 2.14 | V    |

| POR Hysteresis                  | POR3V_Hyst |                |      | 0.25 |      | V    |

#### Table 8. VBOOSTM3V: HIGH SIDE AUXILIARY SUPPLY

| Characteristic Symbol Conditions   |                | Conditions           | Min  | Тур  | Мах  | Unit |

|------------------------------------|----------------|----------------------|------|------|------|------|

| VBSTM3 regulator output<br>voltage | VBSTM3         | Referenced to VBOOST | -3.6 | -3.3 | -2.9 | V    |

| Output current limitation          | llim_VBOOSTM3V |                      |      |      | 200  | mA   |

| Typical VBSTM3 decoupling          | C_VBSTM3       | Referenced to VBOOST |      | 0.47 | 4.7  | μF   |

| capacitor                          | ESR            | Referenced to VBOOST |      |      | 200  | mΩ   |

## Table 9. OSC4M: SYSTEM OSCILLATOR CLOCK

| Characteristic              | Characteristic Symbol Condit |                | Min | Тур | Мах | Unit |

|-----------------------------|------------------------------|----------------|-----|-----|-----|------|

| System oscillator frequency | FOSC4M                       | After trimming | 3.5 | 4.0 | 4.5 | MHz  |

## Table 10. ADC FOR MEASURING VBOOST, VBB, VLED1, VLED2, VTEMP/AGP1, VTEMP/AGP2

| Characteristic                                                            | Symbol        | Conditions | Min   | Тур | Max  | Unit |

|---------------------------------------------------------------------------|---------------|------------|-------|-----|------|------|

| ADC Resolution                                                            | ADC_res       |            |       | 8   |      | Bits |

| Integral Nonlinearity (INL)                                               | ADC_INL       |            | -1.5  |     | +1.5 | LSB  |

| Differential Nonlinearity (DNL)                                           | ADC_DNL       |            | -2.0  |     | +2.0 | LSB  |

| Full path gain error for<br>measurements via VBB,<br>VLEDx, VTEMP, VBOOST | ADC_GAINERROR |            | -3.25 |     | 3.25 | %    |

| Offset at output of ADC                                                   | ADC_OFFSET    |            | -2    |     | 2    | LSB  |

| Time for 1 SAR conversion                                                 | ADCConv       |            |       | 8   |      | μs   |

| ADC full scale for VBB measurement                                        | ADCFS_VBB     |            |       | 40  |      | V    |

| ADC full scale for VLED                                                   | ADCFS_VLED    |            |       | 80  |      | V    |

| ADC full scale for VTEMP                                                  | ADCFS_VTEMP   |            |       | 3   |      | V    |

| ADC full scale for Vboost                                                 | ADCFS_VBOOST  |            |       | 80  |      | V    |

| VLEDx input impedance                                                     | ADC_VLED_INZ  |            | 355   | 500 | 710  | kΩ   |

| VTEMP/AGPx input impedance                                                | ADC_VTAGP_INZ |            | 1.2   | 3   | 4.5  | MΩ   |

# Table 11. BOOSTER

|                 |        |            | SPI/OTP | Normal | Regulation<br>(Note 18) | Window | SHUTDOWN |      |

|-----------------|--------|------------|---------|--------|-------------------------|--------|----------|------|

| Name            | Symbol | Conditions | SETTING | NREGL  | TRGT                    | NREGH  | MAX      | Unit |

|                 |        | Range 0    | [0000]  | 19.5   | 24.5                    | 30     | 49       |      |

|                 |        | Range 1    | [0001]  | 22     | 27                      | 32.5   | 49       |      |

|                 |        | Range 2    | [0010]  | 24     | 29.5                    | 35     | 49       |      |

|                 |        | Range 3    | [0011]  | 27     | 32                      | 38     | 49       |      |

|                 |        | Range 4    | [0100]  | 29     | 35                      | 40.5   | 49       |      |

|                 |        | Range 5    | [0101]  | 31.5   | 37                      | 43.0   | 49       |      |

|                 |        | Range 6    | [0110]  | 34     | 40                      | 45.5   | 59       |      |

| Booster         | VECOT  | Range 7    | [0111]  | 36.5   | 42                      | 48     | 59       | .,   |

| output<br>range | VBOOST | Range 8    | [1000]  | 39.0   | 45                      | 51     | 59       | V    |

|                 |        | Range 9    | [1001]  | 41.5   | 47                      | 53.5   | 59       |      |

|                 |        | Range 10   | [1010]  | 44     | 50                      | 56     | 59       |      |

|                 |        | Range 11   | [1011]  | 46     | 52                      | 57.5   | 59       |      |

|                 |        | Range 12   | [1100]  | 48     | 54.5                    | 60.5   | 62       | 1    |

|                 |        | Range 13   | [1101]  | 49     | 57                      | 65.0   | 67       | 1    |

|                 |        | Range 14   | [1110]  | 52     | 59.5                    | 65.5   | 67       | 1    |

|                 |        | Range 15   | [1111]  | 57.5   | 62                      | 66.5   | 67       | 1    |

18. For further details about the booster table and definitions, please refer to the related section contained in this datasheet.

#### Table 11. BOOSTER (continued)

|                          |           |                     | Booster Oscillator Fre                       | equency [2:0 | <b>)</b> ] |      |        |

|--------------------------|-----------|---------------------|----------------------------------------------|--------------|------------|------|--------|

| Name                     | Symbol    | Conditions          | SPI/OTP Setting                              | Min          | Тур        | Max  | Unit   |

| Booster                  |           | FPWMBOOST = 180 kHz | [011]                                        |              | 11.5       | +12% |        |

|                          |           | FPWMBOOST = 203 kHz | [010]                                        |              | 13         |      |        |

|                          |           | FPWMBOOST = 227 kHz | [001]                                        | 12%          | 14.5       |      |        |

|                          | OSC16M    | FPWMBOOST = 250 kHz | [000]                                        |              | 16         |      | MU     |

| oscillator<br>frequency  |           | FPWMBOOST = 273 kHz | [111]                                        |              | 17.5       |      | MHz    |

|                          |           | FPWMBOOST = 297 kHz | [110]                                        |              | 19         |      |        |

|                          |           | FPWMBOOST = 320 kHz | [101]                                        |              | 20.5       |      |        |

|                          |           | FPWMBOOST = 344 kHz | [100]                                        |              | 22         |      |        |

| Booster PWM<br>frequency | FPWMBOOST | = f_OSC16N          | = f_OSC16M / 64 OSC16M is programmable in SP |              |            |      | PI/OTP |

## Table 11. BOOSTER (continued)

|                 |                   | Boost_ctrl_rate [2:0] |        |      |        |      |  |  |

|-----------------|-------------------|-----------------------|--------|------|--------|------|--|--|

| Name            | Symbol            | OTP Setting Only      | Min    | Тур  | Max    | Unit |  |  |

|                 |                   | [011]                 |        | 86   |        |      |  |  |

|                 |                   | [010]                 |        | 144  |        |      |  |  |

|                 |                   | [001]                 |        | 240  |        |      |  |  |

| Booster control | Desident and sole | [000]                 |        | 400  | 40.50  |      |  |  |

| rate            | Boost_ctrl_rate   | [111]                 | -12.5% | 667  | +12.5% | μs   |  |  |

|                 |                   | [110]                 |        | 1111 | 1      |      |  |  |

|                 |                   | [101]                 |        | 31   | 1      |      |  |  |

|                 |                   | [100]                 |        | 52   | 1      |      |  |  |

## Table 12. BOOSTER PRE-DRIVER

| Name                          | Symbol | Min | Тур | Мах | Unit |

|-------------------------------|--------|-----|-----|-----|------|

| High-side switch<br>impedance | RONHI  |     | 2.5 | 4   | Ω    |

| Low-side switch impedance     | RONLO  |     | 2.5 | 4   | Ω    |

## Table 13. BOOSTER – CURRENT LIMITATION

| Name                                  | Symbol     |                            | Min | Тур | Max | Unit |

|---------------------------------------|------------|----------------------------|-----|-----|-----|------|

| Current limitation threshold voltage  | VLIMTH     | Over full operating range  | 78  | 100 | 122 | mV   |

|                                       | VLIMTH_hot | At T <sub>J</sub> = 160 °C | 85  | 100 | 115 | mV   |

| Threshold<br>voltage<br>hysteresis    | VLIMHYS    |                            | 5   | 10  | 20  | mV   |

| Sense voltage<br>common mode<br>range | CMVSENSE   |                            | -1  |     | 1   | V    |

#### Table 14. ON-CHIP TEMPERATURE SENSOR

| Name                                              | Symbol | Min | Тур        | Max | Unit |

|---------------------------------------------------|--------|-----|------------|-----|------|

| Thermal shut-down level<br>(junction temperature) | TSD    | 163 | 169        | 175 | °C   |

| Thermal warning level<br>(junction temperature)   | TW     |     | TSD –<br>5 |     | °C   |

## Table 15. BUCK REGULATOR – SWITCH

| Name                  | Symbol              | Min | Тур  | Max | Unit |

|-----------------------|---------------------|-----|------|-----|------|

| On resistance         | R <sub>DS(on)</sub> |     | 0.82 | 1.0 | Ω    |

| Overcurrent detection | OCD                 | 1.4 |      | 3   | A    |

| Switching slope       | Trise               |     | 3    |     | V/ns |

|                       | Tfall               |     | 3    |     | V/ns |

## Table 16. BUCK REGULATOR – CURRENT REGULATION

| Name                                                                                                      | Symbol           |                                                                                                                               |                                                                                        | Min             | Тур                      | Max             | Unit   |

|-----------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------|--------------------------|-----------------|--------|

| Current sense<br>comparator threshold<br>voltage setpoint<br>(= end of the BUCK<br>ON-phase) MIN<br>value | VThreshold_MIN   | inte                                                                                                                          | e with 7–bit resolution<br>ernal DAC<br>= [0 0 0 0 0 0 0 0])                           | 25              | 30                       | 35              | mV     |

| Current sense<br>comparator threshold<br>voltage setpoint<br>(= end of the BUCK<br>ON-phase) MAX<br>value | VThreshold_MAX   | inte                                                                                                                          | Programmable with 7-bit resolution<br>internal DAC<br>(bit code 127 = [1 1 1 1 1 1 1]) |                 | 411                      | 451             | mV     |

| Current comparator<br>threshold voltage<br>setpoint step (internal<br>DAC resolution)                     | Delta VThreshold |                                                                                                                               |                                                                                        |                 | 3                        |                 | mV     |

| Name                                                                                                      | Symbol           | SPI/OTP<br>SETTING                                                                                                            |                                                                                        | Min             | Тур                      | Мах             | Unit   |

| Smallest Toff x VLED constant                                                                             | Toff_V_1         | [0000]                                                                                                                        |                                                                                        | 9.9             | 12.4                     | 14.9            |        |

|                                                                                                           | Toff_V_2         | [0001]                                                                                                                        |                                                                                        | 19.8            | 24.5                     | 29.2            |        |

|                                                                                                           | Toff_V_3         | [0010]                                                                                                                        |                                                                                        | 39.6            | 45.9                     | 52.2            |        |

|                                                                                                           | Toff_V_4         | [0011]                                                                                                                        |                                                                                        | 57              | 66.6                     | 76.2            |        |

|                                                                                                           | Toff_V_5         | [0100]                                                                                                                        |                                                                                        | 76.4            | 88                       | 99.6            |        |

|                                                                                                           | Toff_V_6         | [0101]                                                                                                                        |                                                                                        | 96.2            | 110                      | 123.8           |        |

|                                                                                                           | Toff_V_7         | [0110]                                                                                                                        | Value on the right                                                                     | 116.8           | 132                      | 147.2           |        |

|                                                                                                           | Toff_V_8         | [0111]                                                                                                                        | represents                                                                             | 135.8           | 154                      | 172.2           |        |

| Mid range off-time<br>(trimmed @ VLED =<br>55 V)                                                          | Toff_V_9         | [1000]                                                                                                                        | $[VLED * Toff_i]$ $VLED = 55 V and$ $T_J = 155^{\circ}C$                               | 154.5           | 176                      | 197.5           | μs x V |

|                                                                                                           | Toff_V_10        | [1001]                                                                                                                        |                                                                                        | 173.2           | 198                      | 222.8           |        |

|                                                                                                           | Toff_V_11        | [1010]                                                                                                                        |                                                                                        | 191.8           | 220                      | 248.2           |        |

|                                                                                                           | Toff_V_12        | [1011]                                                                                                                        |                                                                                        | 210.6           | 242                      | 273.4           |        |

|                                                                                                           | Toff_V_13        | [1100]                                                                                                                        |                                                                                        | 229.1           | 264                      | 298.9           |        |

|                                                                                                           | Toff_V_14        | [1101]                                                                                                                        | -                                                                                      | 248             | 286                      | 324             |        |

|                                                                                                           | Toff_V_15        | [1110]                                                                                                                        | -                                                                                      | 266.4           | 308                      | 349.6           |        |

| Longest off-time                                                                                          | Toff_V_16        | [1111]                                                                                                                        |                                                                                        | 283.3           | 330                      | 376.2           |        |

|                                                                                                           |                  | VLE                                                                                                                           | ED > 5.4 V                                                                             | To              | ff_i * VLED = CON        | ST              | μs x V |

|                                                                                                           |                  | 6V < VLED <                                                                                                                   | 55 V and Tj is fixed                                                                   | CONST<br>- 8.5% | Toff_i * VLED<br>= CONST | CONST<br>+ 8.5% | μs x V |

| Off-time = f (VLED)                                                                                       | Toff_V_i         | 10V < VLED •                                                                                                                  | < 55 V and Tj is fixed                                                                 | CONST<br>- 7%   | Toff_i * VLED<br>= CONST | CONST<br>+ 7%   | μs x V |

|                                                                                                           |                  | –45°C <tj<155< td=""><td>°C and VLED is fixed</td><td>Toff_i</td><td>* VLED = CONST</td><td>±4%</td><td>μs x V</td></tj<155<> | °C and VLED is fixed                                                                   | Toff_i          | * VLED = CONST           | ±4%             | μs x V |

|                                                                                                           |                  | 1.9 V ≤                                                                                                                       | VLED < 2.6 V                                                                           |                 | 9                        |                 | μs     |

|                                                                                                           |                  | VLE                                                                                                                           | ED < 1.9 V                                                                             |                 | 63                       |                 | μs     |

| Name                        | Symbol                      | Min | Тур | Max | Unit |

|-----------------------------|-----------------------------|-----|-----|-----|------|

| High-level input<br>voltage | VINHI                       | 2   |     |     | V    |

| Low-level input<br>voltage  | VINLO                       |     |     | 0.8 | V    |

| Input leakage<br>resistance | R <sub>pull</sub> (Note 19) | 5   | 10  | 20  | kΩ   |

#### Table 17. 5 V TOLERANT DIGITAL INPUTS (CSB, SDI, SCLK)

19. Pull down resistor (Rpulldown) for SDI and SCLK, pull up resistor (Rpullup) for CSB.

# Table 18. 5 V TOLERANT OPEN-DRAIN DIGITAL OUTPUT (SDO)

| Name                            | Symbol                    |                                                               | Min | Тур | Max | Unit |

|---------------------------------|---------------------------|---------------------------------------------------------------|-----|-----|-----|------|

| Low-voltage<br>output voltage   | VOUTLO                    | $I_{SDO_{out}} = -10 \text{ mA}$ (current flows into the pin) |     |     | 0.4 | V    |

| Equivalent<br>output resistance | R <sub>DS(on)</sub> _DIAG | Lowside switch                                                |     | 20  | 40  | Ω    |

#### Table 19. 3 V TOLERANT DIGITAL INPUTS (TEST1, TEST2)

| Name                        | Symbol                |                     | Min | Тур | Max | Unit |

|-----------------------------|-----------------------|---------------------|-----|-----|-----|------|

| High-level input<br>voltage | VINHI                 |                     | 2   |     |     | V    |

| Low-level input voltage     | VINLO                 |                     |     |     | 0.8 | V    |

| Input leakage<br>resistance | R <sub>pulldown</sub> | Pulldown resistance |     | 20  | 40  | kΩ   |

# Table 20. 3 V PUSH-PULL DIGITAL OUTPUTS (DIAG1, DIAG2)

| Name                            | Symbol              |                                                                | Min | Тур | Max | Unit |

|---------------------------------|---------------------|----------------------------------------------------------------|-----|-----|-----|------|

| High-level<br>output voltage    | VOUTHI              | I <sub>DIAG_out</sub> = 10 mA (current flows out of the pin)   | 2.4 |     |     | V    |

| Low-voltage<br>output voltage   | VOUTLO              | $I_{DIAG_{out}} = -10 \text{ mA}$ (current flows into the pin) |     |     | 0.4 | V    |

| Equivalent<br>output resistance | R <sub>DS(on)</sub> | Lowside switch                                                 |     | 20  | 40  | Ω    |

# Table 21. 40 V TOLERANT DIGITAL INPUTS (LEDCTRL1, LEDCTRL2)

| Name                        | Symbol | Min                      | Тур | Max                      | Unit |

|-----------------------------|--------|--------------------------|-----|--------------------------|------|

| High-level input<br>voltage | VINHI  | 0.7 x<br>V <sub>BB</sub> |     |                          | V    |

| Low-level input<br>voltage  | VINLO  |                          |     | 0.3 x<br>V <sub>BB</sub> | V    |

| Input leakage<br>current    | ILEAK  | -1                       |     | 1                        | μΑ   |

#### Table 22. DIMMING INTERFACE

| Name                                                                                 | Symbol        |                       | Min | Тур  | Max  | Unit |

|--------------------------------------------------------------------------------------|---------------|-----------------------|-----|------|------|------|

| Input dimming<br>frequency                                                           | FDIMMING      |                       | 50  | 1000 | 8000 | Hz   |

| Dimming signal<br>input<br>measurement<br>and output<br>reconstruction<br>resolution | DIMres_IN_OUT |                       |     | 10   |      | μs   |

|                                                                                      |               | SPI/OTP setting [100] |     | 1    |      |      |

| Dimming                                                                              |               | SPI/OTP setting [101] |     | 2    |      |      |

| Frequency                                                                            |               | SPI/OTP setting [110] |     | 3    |      |      |

| Factor<br>(= Output                                                                  |               | SPI/OTP setting [111] |     | 4    |      |      |

| dimming<br>frequency / input                                                         | DFF[2:0]      | SPI/OTP setting [000] |     | 5    |      |      |

| dimming                                                                              |               | SPI/OTP setting [001] |     | 6    |      |      |

| frequency)                                                                           |               | SPI/OTP setting [010] |     | 7    |      |      |

|                                                                                      |               | SPI/OTP setting [011] |     | 8    |      |      |

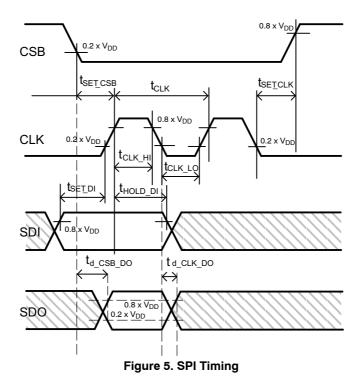

## Table 23. SPI INTERFACE

| Name                                                     | Symbol               | Min | Тур | Мах | Unit |

|----------------------------------------------------------|----------------------|-----|-----|-----|------|

| SPI clock period                                         | t <sub>CLK</sub>     | 1   |     |     | μs   |

| SPI clock high time                                      | t <sub>CLK_HI</sub>  | 100 |     |     | ns   |

| SPI clock low time                                       | t <sub>CLK_LO</sub>  | 100 |     |     | ns   |

| SDI set up time, valid data before rising edge of CLK    | tset_DI              | 50  |     |     | ns   |

| SDI hold time, hold data after rising edge of CLK        | tHOLD_DI             | 50  |     |     | ns   |

| CSB high time                                            | tcs_ніgh             | 2.5 |     |     | μs   |

| CSB set up time, CSB low before rising<br>edge of CLK    | tset_csb             | 1   |     |     | μs   |

| CLK set up time, CLK low before rising edge of CSB       | tSET_CLK             | 100 |     |     | ns   |

| Delay time from falling edge of CSB to a valid DO signal | $Td_{CSB}DO$         | 50  |     |     | ns   |

| Delay time from falling edge of CLK to a valid DO signal | Td <sub>CLK_DO</sub> | 50  |     |     | ns   |

#### DETAILED OPERATING AND PIN DESCRIPTION

#### SUPPLY CONCEPT IN GENERAL

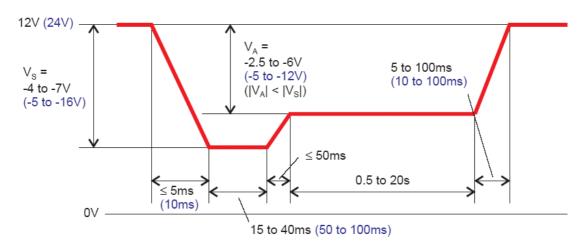

Low operating voltages become more and more required due to the growing use of start stop systems. In order to respond to this necessity, the NCV78663 is designed to support power–up with a minimum guaranteed  $V_{BB} = 5$  V.

Figure 6. Cranking Pulse (ISO7637–1): System has to be Fully Functional (Grade A) from  $V_s = 5 V$  to 28 V

#### **VDRIVE Supply**

The VDRIVE supply voltage is the primary supply for the complete chip and sustains the VREG3V (which provides the VDD voltage, used by the internal circuitry) and the BOOST PREDRV, which generates the VGATE, used to switch the booster MOSFET.

In order to support low VBB battery voltages and long crank pulse drops, the VDRIVE supply takes its energy from the source with the highest output voltage, either from:

- the VREG10V supply, which derives its energy from the VBB input.

- the VBOOST\_AUXSUP, which gets its energy from the VBOOST path.

Under normal operating conditions, VREG10V is the highest and all the internal device plus gate driver energies are supplied via VBB.

At power-up, the VREG3V (for VDD) is supplied through the VREG10V from the VBB input pin. Due to the low drop-out, the chip starts up from VBB  $\ge$  5 V and, the boost voltage starts to build-up.

In case VBB drops below the regulator margin of VREG10V, the VDRIVE supply is then sustained by the VBOOST\_AUXSUP regulator: after this occurs, VBB can drop below 5 V and lower, as long as the booster is capable to generate sufficient voltage.

<u>Note</u>: Powering the device via the VBOOST\_AUXSUP will produce an extra power dissipation linked to the related linear drop (VBOOST-VBOOST\_AUXSUP), which must be taken into account during the thermal design.

#### **VDD Supply**

The VDD supply is the low voltage digital and analog supply for the chip and takes energy from VDRIVE. Due to the low drop-out regulator design, VDD is guaranteed already from low VDRIVE voltages (see Table 7). The Power On Reset circuit (POR) monitor is based on the VDD voltage.

#### VBOOSTM3V Supply

The VBOOSTM3V is the high side auxiliary supply for the gate drive of the buck regulators' integrated high-side P-MOSFET switches. This supply receives energy directly from the VBOOST pin.

## INTERNAL CLOCK GENERATION

Two internal clocks are fully internally generated without the need for any further trimming by the user. Their accuracy is guaranteed under full operating conditions and independent from external component selection.

#### **OSC4M Clock**

The OSC4M clock is the system clock and factory trimmed to 4 MHz. It provides a time base for the entire digital part, except the boost converter PWM and the SPI clock. For details about the accuracy see Table 9.

#### OSC16M Clock

The OSC16M clock is the booster reference clock. It is factory trimmed and user selectable between typical 11.5 MHz and 22 MHz. The booster PWM frequency is 1/64 of the OSC16M frequency, thus between 179.7 kHz and 343.8 kHz. Refer to Table 11 for accuracy details.

# ADC

#### General

The built-in analog to digital converter (ADC) is an 8-bit capacitor based successive approximation register (SAR).

This embedded peripheral can be used to provide the following measurements to an external Micro Controller Unit (MCU):

- VBOOST voltage

- VBB voltage

- VLED1, VLED2 voltages

- VTEMP\_AGP1, VTEMP\_AGP2 voltages

The internal NCV78663 ADC state machine samples all the above channels automatically, taking care for setting the analog MUX and storing the converted values in memory. The device LED diagnostics and the digital boost controller make use of the values as inputs.

To remark that the VLEDx (1, 2) lines are sampled only when the respective LED output is activated and the last sampled value is kept, until it is overwritten (refreshed) by a new one.

An external MCU can read-out all measured values via the SPI interface in order to take application specific decisions. Please note that the MCU SPI commands do not interfere with the internal ADC state machine sample and conversion operations: the MCU will always get the last available data at the moment of the register read.

Each new boost voltage sample occurs at 17  $\mu$ s worst case rate. VLED1 and VLED2 voltages are typically sampled at a rate of about 52  $\mu$ s (when the buck switches are on), while VTEMP\_AGP1 and VTEMP\_AGP2 are continuously sampled at a rate of 4 ms. The battery voltage is sampled typically each 108  $\mu$ s.

#### **ADC Channel Selection**

The ADC channel selection readout is done via the SPI-CR11 register (the part "ADC\_Sel" behaves as a pointer to the requested data), while the SPI–SR3 registers will hold the data (see section SPI Address Map). When polling the same channel over time, there is no need to refresh the address field, as the SPI–SR3 register will be automatically refreshed with the latest available data.

| ADC_SEL[2:0] | VBOOST | VBB | VLED1  | VLED2  | VTEMP_AGP1 | VTEMP_AGP2 |

|--------------|--------|-----|--------|--------|------------|------------|

| 000          | 1      | 0   | 0      | 0      | 0          | 0          |

| 001          | 0      | 1   | 0      | 0      | 0          | 0          |

| 010          | 0      | 0   | 1      | 0      | 0          | 0          |

| 011          | 0      | 0   | 0      | 1      | 0          | 0          |

| 100          | 0      | 0   | 0      | 0      | 1          | 0          |

| 101          | 0      | 0   | 0      | 0      | 0          | 1          |

| 110          |        |     | Do not | select |            |            |

| 111          |        |     | Do not | select |            |            |

#### **Battery Voltage ADC Measurement**

The battery voltage is sampled making use of the device supply VBB-pin. This measurement is also used by the boost controller for the closed loop voltage regulation to set the maximum duty cycle depending on the battery level: the lower the level, the higher the maximum duty cycle allowed.

The (8 bit) conversion ratio is 40/255 (V/dec) = 0.157 (V/dec) typical. The external MCU can make use of the measured VBB value to monitor the status of the module supply and also for a different or more complex power de-rating algorithm than the one embedded in the NCV78663 (see Section Automatic Power De-rating).

#### LED String Voltage ADC Measurement

The voltage at the pins VLEDx (1, 2) is measured. Their 8 bit conversion ratio is 80/255 (V/dec) = 0.318 (V/dec) typical.

This is also used by the diagnostics controller to detect OpenLEDx, ShortLEDx and IndShortLEDx.

The external MCU can use the measured VLED value for a dedicated individual short LED algorithm, more complex than the threshold decision based embedded in the LED DRIVER.

# LED Temperature Feedback / ADC General Purpose Inputs Measurement

Measures the voltage at the pins VTEMP/AGPx (1,2). The typical application would be sensing the transducer voltage related to LED modules' temperature, so that the external MCU can use the information for protecting the LED strings from overheating, or to adapt the luminous flux to the temperature. A common technique is to use an NTC pulled up to the chip VDD.

The VTEMP/AGPx typical sample rate is 4 ms. Please note that these pins are ADC *general purpose* and can be also used to sample references, or other application–related relatively slowly varying voltages.

The VTEMP/AGPx input dynamic range is given by the VDD voltage and no higher value can be forced to these pins.

Their (8 bit) conversion ratio is 3/255 (V/dec) = 11.76 (mV/dec) typical.

#### **Boost Voltage ADC Measurement**

This measure refers to the boost voltage at the VBOOST-pin, with an 8bit conversion ratio of 80/255 (V/dec) = 0.318 (V/dec) typical. This measurement is also used by the boost controller and by the diagnostics controller to detect Boost under-voltage (BoostUV).

#### **BOOST CONTROLLER**

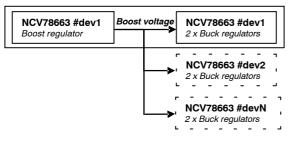

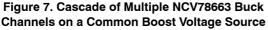

The NCV78663 features one common booster stage for the two integrated buck current regulators. In addition, optional external buck regulators belonging to other devices can be cascaded to the same boost voltage source as well as exemplified in the picture below.

The booster stage provides the required voltage source for the LED string voltages out of the available battery voltage. Moreover, it filters out the variations in the battery input current in case of LED strings PWM dimming.

For nominal loads, the boost controller will regulate in *continuous mode* of operation, in order to maximize system power efficiency and to have the lowest possible input ripple current (with "continuous mode" it is meant that the supply current does not go to zero while the load is activated).

In case of low loads or low dimming duty cycle values, discontinuous mode can occur: this means the supply current can swing from zero when the load is off to the required peak value when the load is on, while keeping the required input average current through the cycle. In such situations, the total efficiency ratio may be lower than the theoretical optimal. However, as also the total losses will at the same time be lower, there will be no impact on the thermal design.

#### **Booster Voltage Range Selection**

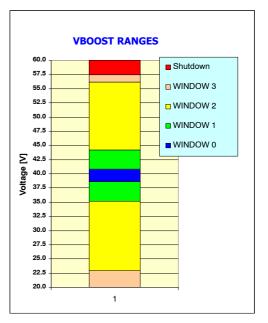

The boost voltage can be programmed in one of the sixteen (16) available ranges by means of the SPI register booster output range [3:0] (or OTP in NCV78663 stand alone mode). Each of the ranges has its typical regulation level, called target ( $V_{BOOST\_TRGT}$ ) and a so defined normal regulation region, or "window 1", whose limits are NREGL and NREGH.

In normal regulation mode, the boost voltage  $V_{\text{BOOST}}$  time average will always match the target, while its instantaneous value is free to swing between NREGL and NREGH.

The absolute maximum voltage for each range is defined as shutdown level (V<sub>SHUTDOWN</sub>). For V<sub>BOOST</sub>  $\geq$ V<sub>SHUTDOWN</sub>, the MOSFET PWM (VGATE) will be switched off. The shutdown level can be chosen to minimize the needed voltage rating (size/cost) of the externals.

The range should be selected with the appropriate NREG levels for the application. In particular, for proper operation of the LED strings, the selected boost voltage range "xx" must be such that NREGL\_xx is higher than the maximum LED string voltage used.

More information about the boost control loop is given in the following section.

#### **Booster Regulation Closed Loop Details**

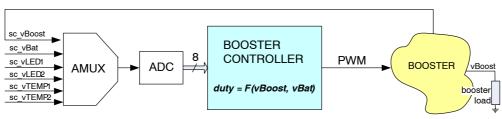

The NCV78663 features a digital voltage mode controller designed to regulate the boost voltage around the target defined by the selected range. This closed loop system samples feedback signals and drives the boost MOSFET gate by PWM as shown in the next figure.

Figure 8. NCV78663: Boost Voltage Regulation Closed Loop

The regulation feedback is mainly based on the  $V_{BOOST}$  sampled value itself and only partially on the battery value seen at the device pin (VBB). Both signals are sampled by the NCV78663 internal ADC in the way described in the relative section. The boost voltage is regulated with a fixed frequency / variable duty cycle scheme.

The duty cycle (DC) is obtained internally out of a 6-bit counter (DC =  $0 \div 63$ ). DC = 63 corresponds to duty cycle

100% and DC = 0 corresponds to duty cycle 0%. However, 100% is never allowed and the maximum duty cycle corresponds to a parameter defined as  $DC_{max}$ . In addition, except in case of shutdown, the duty cycle is low-bounded to a value called  $DC_{min}$ , which is hard coded to value of "4" (4/63 = 6.3%) and is the same for all selectable booster ranges.

$DC_{max}$  is fetched from an internal ROM table and depends on the sampled battery voltage, this last divided in ranges. The general rule is the higher the battery voltage, the lower the  $DC_{max}$  allowed. This is intended to reduce boost voltage and input current overshoots when the battery voltage goes too high. For low battery voltages, the  $DC_{max}$  is increased to permit more current inflow to allow achieving the required output power. The  $DC_{max}$  value 61 (96.8%) is never exceeded even in case of ultra-low battery.

Eight battery ranges are available as shown below:

#### Table 24. NCV78663 BATTERY RANGES FOR BOOST CONTROLLER

| VBB_RNG0 | VBB_RNG1 | VBB_RNG2  | VBB_RNG3  | VBB_RNG4  | VBB_RNG5  | VBB_RNG6  | VBB_RNG7  |

|----------|----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 0 ÷ 5 V  | 5 ÷ 10 V | 10 ÷ 16 V | 16 ÷ 20 V | 20 ÷ 24 V | 24 ÷ 30 V | 30 ÷ 35 V | 35 ÷ 40 V |

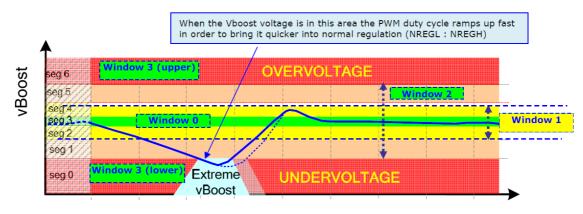

Each Vboost ADC sample is compared within voltage sections called "windows". For each selected range, four different windows, plus a shutdown safety level, are present:

- A. Window 0. This is one of the "normal modes" of the control law. When the sampled Vboost falls in this region, there is no change in the PWM duty cycle. For all boost ranges, the width of this window is 2 V. The central value of this window is corresponding to  $V_{\text{BOOST}}$  TRGT, reported in the middle column of Table 11.

- B. Window 1. This is the most frequent status of the control law and this is what we refer to simply as general "normal mode". When in this region, the PWM is corrected by "±1dec" (= ±1.58%) with a cadency corresponding to the *boost control rate*. The sign of the correction will be "plus" if the voltage is below window 0; "minus" otherwise. Each correction is intended to bring Vboost towards the  $V_{\text{BOOST\_TRGT}}$ . The size of any window 1, ranging in Table 11 from NREGL to NREGH, is typically about 10 V.

- C. Window 2. When in this region, the PWM duty is adapted by " $\pm$ 2" (=  $\pm$ 3.17%) with a cadency corresponding to the *boost control rate*, with the intention to bring Vboost towards the target. As the distance from the target is higher than in point B., the correction is stronger.

- D. Window 3. When in this range the controller works in limitation mode. The PWM duty cycle is rapidly modified every two PWM periods: in the upper threshold, the duty cycle is decreased towards the  $DC_{max}$  trying to avoid reaching the shutdown level, whereas in the lower threshold side the duty cycle is ramped up towards the  $DC_{min}$  "pumping in" energy from the supply to avoid LED blank out because of lack of voltage headroom.

- E. Shutdown. This is a safety level to avoid overvoltage at which the MOSFET gate is shut off (duty cycle = 0%, or DC = 0). This is corresponding to column "MAX" rating in

Table 11. <u>Note</u>: this "MAX rating" corresponds also to the maximum booster output voltage in case of unloaded stage (buck regulators off). A graphical explanation is given in the figure below by referring to boost range 06 as an example.

Figure 9. NCV78663: Boost Controller Voltage Segments When Boost\_RNG = 6 is Selected

#### **REMARKS and PRACTICAL CONSIDERATIONS**

For a well sized booster system with the NCV78663, the controller will operate inside window 1 (or window 0), thus:

$V_{BOOST TRGT} - 5 V < V_{BOOST} < V_{BOOST TRGT} + 5 V$

An exception might be at booster load start–up, when its output power passes for the first time from zero (unloaded) to maximum (application target). In this case, the voltage is allowed to drop in the low threshold of window 3 and after a first settling transient, the regulation will enter normal mode (window 1).

Figure 10. NCV78663: Boost Voltage Possible Behavior at First Full Power Load Activation

In order to guarantee the regulation in WINDOW 1 throughout operating conditions and dimming, a total boost capacitance Cboost  $\geq 50 \ \mu\text{F}$  is recommended for medium to high application power. For further details about capacitance sizing, please refer to application notes.

Please note that the boost voltage regulation loop is not affected whether a continuous or discontinuous mode of operation (E.G. low dimming duty cycle) is taking place.

#### **Booster PWM Frequency**

The booster controller is working with a constant frequency and variable duty cycle to control the booster voltage.

The operating frequency is user selectable with three SPI/OTP setting bits (Section OSC16M Clock), in order to optimize the booster inductor's size and EMC aspects.

#### **Booster Disable Function**

In some cases, it is useful to disable the booster by means of the BOOSTER\_DIS bit. For instance if:

- the NCV78663 uses a shared booster from another device,

- it is desired to start the hardware module from a complete off state, or to minimize energy consumption in some particular operating modes.

#### External Boost FET Pre-driver

The external boost MOSFET is directly controlled by the integrated pre-driver with slope-control to attenuator EMC emissions. Due to the cycle by cycle current limitation, the peak-currents in the MOSFET are reduced, resulting in optimized system efficiency. Also for efficiency reasons, it is important to select a MOSFET with low gate-charge.

The pre-driver is supplied by the VDRIVE supply (typical 10 V) supporting standard FETs.

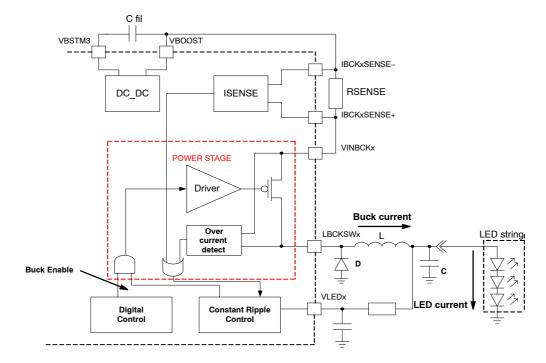

#### **Buck Regulator**

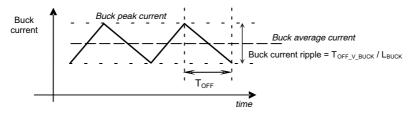

The buck regulator is the current source to the LED string. This block controls the peak current and also incorporates a constant ripple control circuit to ensure also stable average current through the LED string.

The formula that defines the total ripple current over the buck inductor is hereby reported:

$$\Delta I_{BUCK_pkpk} = \frac{T_{OFF} \times (V_{LED} + V_{DIODE})}{L_{BUCK}}$$

$$\approx \frac{T_{OFF} \times V_{LED}}{L_{BUCK}} = \frac{T_{OFF_v_BUCK}}{L_{BUCK}}$$

In the formulas above  $T_{OFF}$  represents the buck switch off time,  $V_{LED}$  is the LED voltage feedback sensed at the NCV78663 pin and  $L_{BUCK}$  is the buck inductor value.

Figure 11. Buck Regulator Controlled Average Current

In order to achieve a constant ripple current value, the NCV78663 varies the  $T_{OFF}$  time inversely proportional to the  $V_{LED}$  sensed at the device pin, according to the factor  $T_{OFF}$  v <sub>BUCK</sub> programmable by SPI/OTP (see Table 16).

As a consequence to the constant ripple control and variable off time, the buck switching frequency is dependent on the boost voltage and LED voltage in the following way:

$$\begin{split} f_{BUCK} &= \frac{V_{BOOST} - V_{LED}}{V_{BOOST}} \cdot \frac{1}{T_{OFF}} = \\ &= \frac{V_{BOOST} - V_{LED}}{V_{BOOST}} \times \frac{V_{LED}}{T_{OFF\_V\_BUCK}} \end{split}$$

The buck average current is described by the formula:

$$I_{BUCK AVG} = I_{BUCK peak} - \frac{\Delta I_{BUCK_pkpk}}{2}$$

The parameter  $I_{BUCK\_peak}$  is programmable through the device by means of the internal comparator threshold (Table 16) over the external sense resistor RSENSE:

$$K_{\text{peak}} = \frac{V_{\text{Threshold}}}{R_{\text{SENSE}}},$$

where  $V_{threshold}$  is the current comparator internal set–point reference (Table 16).

$V_{Threshold} = V_{Threshold MIN} + Delta_V_{Threshold} \times$

× Current\_Setting\_SPI(dec).

The item "Current\_setting\_SPI (dec)" corresponds to the value written in the related for the "x" string, programmable from 0 to 127 (7bits). Please refer to Tables 26 and 27 for more information.

The full buck circuit diagram follows:

I<sub>BUC</sub>

Figure 12. Buck Regulator Complete Schematics

Independently from the peak current setting, there is also an overcurrent detection (fixed threshold) which is measured over the internal buck MOSFET. See Table 15.

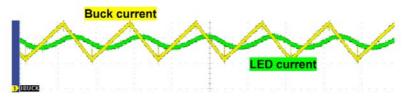

The LED average current in time is equal to the buck time average current. Therefore, to achieve a given LED current target, it is sufficient to know the buck peak current and the buck current ripple.

For what concerns the LED ripple current, this is defined by the Buck inductor ripple current, the buck capacitor and the total LED string equivalent impedance. A rule of thumb is to count a minimum of 50% ripple reduction by means of the capacitor  $C_{BUCK}$  and this is normally obtained with a ceramic component ranging from 100 nF to 470 nF. The following figure reports a typical example. The use of  $C_{BUCK}$  is a cost effective way to improve EMC performances without the need to increase the value of  $L_{BUCK}$ , which would be certainly a more expensive action.

Figure 13. LED Current AC Components Filtered Out By the Output Impedance (scope snapshot)

# DIMMING

The chip supports both analog and digital or PWM dimming. Analog dimming is done by controlling the LED current during operation. This can be done by means of changing the peak current level and/or the Toff\_V constants (see Buck Regulator – Current regulation) by SPI commands.

In this section, we only describe the PWM dimming as this is the preferred method to maintain the desired LED color temperature for a given current rating.

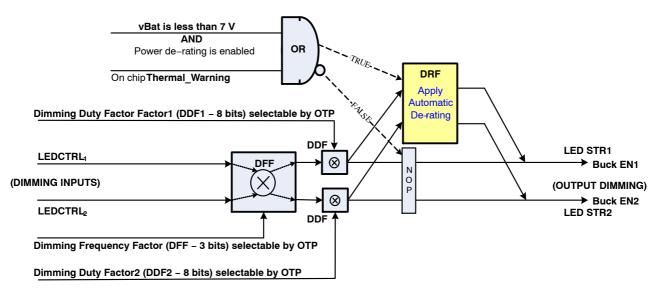

In digital dimming, the LED current waveform frequency is constant and the duty cycle is set according to the required light intensity. The two independent control inputs LEDCTRLx handle the dimming signals for the related channel. More details in the following section.

Figure 14. NCV78663 Internal Digital (PWM) Dimming Structure

The dimming signal of each LED string is controlled via the respective LEDCTRLx input; the PWM there applied is sampled and converted into an output PWM signal used for enabling the buck channel driving the LEDx string (the internal buck MOSFET enabled signal is called BUCK\_ENx).

The BUCK\_ENx signal frequency is obtained multiplying the input frequency by the Dimming Frequency Factor (DFF). Increasing the dimming frequency is very useful to avoid the *beats effect*. In addition, higher dimming frequency reduce the dimming boost voltage swings for a given output booster capacitor.

The BUCK\_ENx duty cycle is equal to the input duty cycle times the internal scaling factors: the Dimming Duty Factor (DDF) and the Dimming Derating Factor (DRF). This last is automatically set by the device in case a power de-rating condition is occurring (see section Automotive Power De-rating). The DRF is applied to both channels simultaneously.

The DDFx is instead individually programmable for each buck channel and can range from 0% to 100%. The default DDFx value is written in OTP, while a microcontroller can vary the present value via SPI when the application is running. The formula which links the output dimming duty factor for the channel "x" to the internal SPI register is:

$$DutyFactor_{x} = 100 \times \frac{255 - DDF_{SPI\_REGx}}{255}$$

or equivalently:

$$\text{DDF}_{\text{SPI}_{\text{REGx}}} = 255 \times \frac{100 - \text{DutyFactor}_{x}}{100}$$

The following formula summarizes the effects on the dimming duty cycle for the LED STRING "x":

$\mathsf{BuckENx}_{\mathsf{DUTY}} = \mathsf{DutyIN}_{\mathsf{LEDCTRLx}} \times \mathsf{DutyFactor}_{\mathsf{x}} \times \mathsf{DRF}$

Where DutyIN<sub>LEDCTRLx</sub> represents the input duty cycle provided by the external logic (or MCU) at the LEDCTRLx input.

As the input signal at the LEDCTRLx is sampled by the NCV78663 digital, a delay must elapse for each change in frequency and/or duty cycle before the device can reconstruct a new valid BUCK\_ENx. The maximum delay for a frequency change is four periods of the input signal, whereas for a duty cycle change only, with any given frequency, up to two periods of the input signal can be needed.

To detect an input duty cycle of 100% ("long one" = LEDx continuously ON), an input period higher than 40 ms is

required. Vice versa, starting from a 100% duty cycle condition, in order to detect a 0% input signal (LEDx continuously OFF), up to 2 ms may be required.

Using a 100% input duty cycle will by nature remove the external dimming frequency reference to the device. In such a case, if a duty cycle scaling (DDFx or DRF) is active, the internal frequency dimmer timer is used. Its base frequency is 500 Hz x DFF. This feature can be exploited as a method to avoid the use of an external frequency generator even when dimming is really intended: an hint for the application is then to tie (or pull up) the LEDCTRLx pins to the VBB pin and to set the wanted dimming parameters just by means of SPI. A DDFx = 0% (255dec) will always secure to turn off the LEDx strings across operating conditions.

To note how the time resolution of both the input LEDCTRLx sampler and the BUCK\_ENx output reconstructed signals is 10 µs nominal (see Table 22): this

value corresponds to the smallest resolution obtainable for digital dimming.

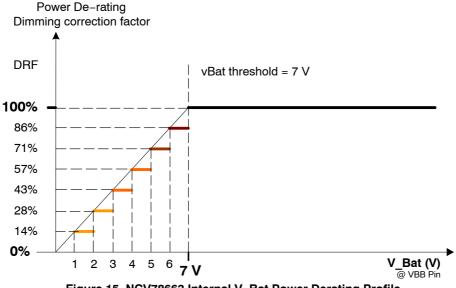

#### Automatic Power De-rating

The LED output power can be automatically de-rated by decreasing the calculated output duty cycle in case of detected extreme conditions: either low battery voltage or active on-chip Thermal Warning.

The NCV78663 features an embedded automatic power derating function based on the battery voltage which can be enabled or disabled by OTP/SPI (PWRDERATE\_DIS bit, see SPI map). The battery voltage measurement is automatically performed by the device sampling of the VBB pin. In case a protection diode in front of the VBB is used, its voltage drop and the discharge delay of the external capacitor in parallel to the pin have to be taken into account. The V\_BAT power derating is implemented according to the graph below:

Figure 15. NCV78663 Internal V\_Bat Power Derating Profile

When the de-rating condition disappears the output duty will go back to 100% of the calculated output duty. The de-rating process is applied on both led channels simultaneously.

In case of on-chip Thermal Warning, the calculated output duty cycle is further scaled to 75% of its previous calculated value (*thermal derating*). Then when the junction temperature falls below the Thermal Warning level, the thermal de-rating condition is automatically exited. The warning bit in SPI status register remains activated until reset via an SPI read-command.

**Example**: V\_Bat de-rating and thermal derating occurring at the same time. For instance, 6 V < VBB < 7 V and thermal warning: the total de-rating factor would be 86% x 75% = 64.5%.

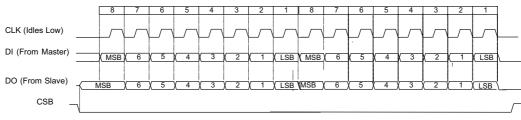

#### SPI INTERFACE

#### Description

The serial peripheral interface (SPI) is used to program the default start-up operating parameters in OTP via the ZAP! operation. Optionally, it allows an external microcontroller (MCU) to communicate with the device to read-out status information and to change operating parameters after power-up.

The NCV78663 SPI transfer packet size is 16 bits. During an SPI transfer, the data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line (CLK) synchronizes shifting and sampling of the information on the two serial data lines: SDO and SDI. The DO signal is the output from the Slave, and the SDI signal is the output from the Master. A slave select line (CSB) allows individual selection of a slave SPI device in a time multiplexed multiple–slave system. The CSB line is active low. If an NCV78663 is not selected, SDO is in high impedance state and it does not interfere with SPI bus activities. Since NCV78663 always clocks data out on the

falling edge and samples data in on rising edge of clock, the MCU SPI port must be configured to match this operation. The SPI CLK idles low between transferred frames. The diagram below is both a master and a slave timing diagram since CLK, DO and DI pins are directly connected between the Master and the Slave.

<u>Note</u>: The data transfer from the shift register into the locally used registers, interpretation of the data is only done at the rising edge of CSB.

The Data that is send over to the shift register to be transmitted to the external MCU is sampled at the falling edge of CSB, just at the moment the transmission starts.

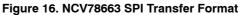

The implemented SPI block allows interfacing with standard MCUs from several manufacturers. When interfaced, the NCV78663 acts always as a Slave and it cannot initiate any transmission. The MCU is instead the master, able to send read or write commands. The NCV78663 SPI allows connection to multiple slaves by

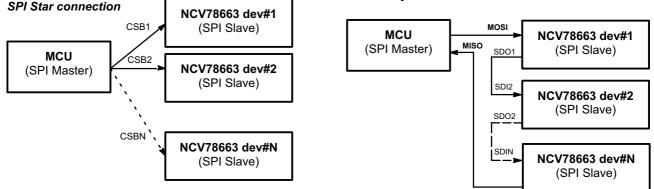

means of both star connection (one individual CSB per Slave, while SDI, SDO, CLK are common) or by means of daisy chain (common CSB signal and clock, while the data lines are cascaded as in the figure). An SPI *star connection* requires a bus = (3 + N) total lines, where N is the number of Slaves used, the SPI frame length is 16 bits per communication. Regarding the SPI *daisy chain connection*, the bus width is always four lines independently on the number of slaves. However, the SPI transfer frame length will be a multiple of the base frame length so N x 16 bits per communication: the data will be interpreted and read in by the devices at the moment the CSB rises.

Figure 17. NCV78663 SPI Star vs. Daisy Chain Connection

#### **Transfer Format**

All SPI commands (to SDI pin of NCV78663) from the Master consist of one "address/command byte" (MSByte or MSB) and one "data byte" (LSByte or LSB).

The address/command byte is the MSB and is divided into two nibbles (2 x 4 bits). Each nibble is an address pointing to the 16 bytes address space of the NCV78663 SPI register map (see related section) and in the same time it is interpreted also as a command (explanation given below). Two types of registers exist in the SPI address space: Control and Status registers. Control registers are read/write accessible whereas Status registers are only read accessible. The type of the register is determined by the address decoder of the SPI and depends on its position in the address space.

Three command-types can be distinguished: "Write to a control register", "Read from a control register" and "Read from a status register".

• Writing to a control register is accomplished only if the address of the target register appears in the upper address/command nibble. The contents of the data-byte will be copied in the control register.

- Reading from a control register is accomplished by putting its address in the lower address/command nibble. The data byte has no function for this command.

- Reading from a status register is accomplished by putting its address either in the upper or in the lower

address/command nibble. The data byte has no function for this command.

The response (SDO) on the commands from the first frame is always two bytes long and is located in the subsequent SPI frame. The possible combinations of SDI/SDO and their use are summarized in the following table:

|    | NC                                    | V78663 received input: SDI                  |                           |                        | NCV78663 response: SD     | 0                                                              |

|----|---------------------------------------|---------------------------------------------|---------------------------|------------------------|---------------------------|----------------------------------------------------------------|

|    | SPI 16bit Frame 01<br>MSB high-nibble | SPI 16bit Frame 01<br>MSB <i>low-nibble</i> | SPI 16bit Frame 01<br>LSB | SPI 16bit Frame 02 MSB | SPI 16bit Frame 02<br>LSB |                                                                |

| ID | ADDR_CMD [7:4]                        | ADDR_CMD [3:0]                              | DATA[7:0]                 | ADDR_CMD[7:0]          | DATA[7:0]                 | Comments                                                       |

| 1  | ACR1                                  | ACR2                                        | DICR1                     | DOCR1                  | DOCR2                     | Write to CR1 content of data field (DICR1) and read CR2        |

| 2  | ACR1                                  | ASR1                                        | DICR1                     | DOCR1                  | DOSR1                     | Write to CR1 content of data<br>field (DICR1) and read<br>ASR1 |

| 3  | ASR1                                  | ACR1                                        | XXh                       | DOSR1                  | DOCR1                     | Read both ASR1 and ACR1                                        |

| 4  | ASR1                                  | ASR2                                        | XXh                       | DOSR1                  | DOSR2                     | Read both ASR1 and ASR2                                        |

#### Table 25. SPI FRAME FORMAT TRANSFER

LEGENDA:

- ACRx = Address of Control Register x

- ASRx = Address of Status Register x

- DICRx = Data Input of Control Register x

- DOCRx/DOSRx = Data Output of corresponding Register.

- XXh = any byte

<u>SPI Command Example</u>: Write "data value 255" (= 0xFF hex) to control register at "address 1" (= 0x01 hex) and read control register at "address 4" (= 0x04 hex)

#### SDI Line (binary representation)