One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

# Using the ADuCM362/ADuCM363 Low Power, Precision Analog Microcontroller with Dual Sigma-Delta ADCs, ARM Cortex-M3

#### **SCOPE**

This user guide provides a detailed description of the ADuCM362/ADuCM363 functionality and features.

Note that, throughout this reference manual, multifunction pins, such as P1.0/IRQ3/PWMSYNC/EXTCLK, are referred to either by the entire pin name or by a single function of the pin, for example, P1.0, when only that function is relevant.

#### **DISCLAIMER**

Information furnished by Analog Devices, Inc., is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# **TABLE OF CONTENTS**

| Scope                                             | System Exceptions and Peripheral Interrupts       | 56  |

|---------------------------------------------------|---------------------------------------------------|-----|

| Disclaimer1                                       | Cortex-M3 and Fault Management                    | 56  |

| Revision History                                  | External Interrupt Configuration                  | 59  |

| Using the ADuCM362/ADuCM363 Hardware User Guide 4 | Interrupt Memory Mapped Registers                 | 59  |

| Number Notations4                                 | DMA Controller                                    | 64  |

| Register Access Conventions 4                     | DMA Features                                      | 64  |

| Acronyms and Abbreviations4                       | DMA Overview                                      | 64  |

| Introduction to the ADuCM362/ADuCM3635            | DMA Operation                                     | 64  |

| Main Features of ADuCM362/ADuCM3636               | Error Management                                  | 64  |

| Memory Organization                               | Interrupts                                        | 65  |

| Clocking Architecture                             | DMA Priority                                      | 65  |

| Clocking Architecture Features                    | Channel Control Data Structure                    | 65  |

| Clocking Architecture Block Diagram9              | Control Data Configuration                        | 66  |

| Clocking Architecture Overview10                  | DMA Transfer Types (CHNL_CFG[2:0])                | 67  |

| Clocking Architecture Operation10                 | Address Calculation                               | 69  |

| Clocking Architecture Memory Mapped Registers10   | DMA Memory Mapped Registers                       | 72  |

| Power Management Unit                             | Flash Controller                                  | 85  |

| Power Management Unit Features                    | Flash Controller Features                         | 85  |

| Power Management Unit Overview16                  | Flash Controller Overview                         | 85  |

| Power Management Unit Operation16                 | Flash Memory Organization                         | 85  |

| Power Management Unit Memory Mapped Registers 17  | Writing to Flash/EE Memory                        | 86  |

| Cortex-M3 Processor                               | Erasing Flash/EE Memory                           | 86  |

| Cortex-M3 Processor Features                      | Flash Controller Performance and Command Duration | 87  |

| Cortex-M3 Processor Overview                      | Flash Protection                                  | 87  |

| Cortex-M3 Processor Operation                     | Flash Controller Failure Analysis Key             | 88  |

| Related Documents                                 | Flash Integrity Signature Feature                 | 88  |

| ADC Circuit                                       | Integrity of the Kernel                           | 88  |

| ADC Circuit Features                              | Abort Using Interrupts                            | 88  |

| ADC Circuit Block Diagram21                       | Flash Controller Memory Mapped Registers          | 89  |

| ADC Circuit Overview21                            | Reset                                             | 97  |

| ADC Circuit Operation                             | Reset Features                                    | 97  |

| Other ADC Support Circuits26                      | Reset Operation                                   | 97  |

| Other ADC Details                                 | Reset Memory Mapped Registers                     | 98  |

| ADC Circuit Memory Mapped Registers36             | Digital I/Os                                      | 99  |

| DAC51                                             | Digital I/Os Features                             | 99  |

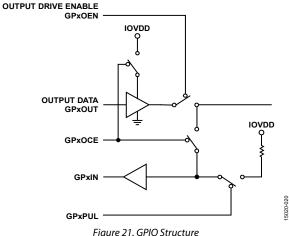

| DAC Features51                                    | Digital I/Os Block Diagram                        | 99  |

| DAC Overview51                                    | Digital I/Os Overview                             | 99  |

| DAC Operation                                     | Digital I/Os Operation                            | 99  |

| DAC DMA Operation53                               | Digital Port Multiplex                            | 101 |

| DAC Memory Mapped Registers54                     | GPIO Memory Mapped Registers                      | 102 |

# UG-1048

# ADuCM362/ADuCM363 Hardware Reference Manual

| I <sup>2</sup> C Serial Interface           | General-Purpose Timers Overview146                |

|---------------------------------------------|---------------------------------------------------|

| I <sup>2</sup> C Features                   | General-Purpose Timers Operation146               |

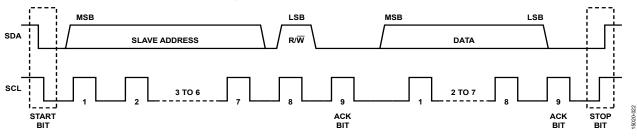

| I <sup>2</sup> C Overview105                | General-Purpose Timers Memory Mapped Registers148 |

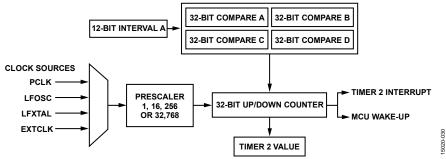

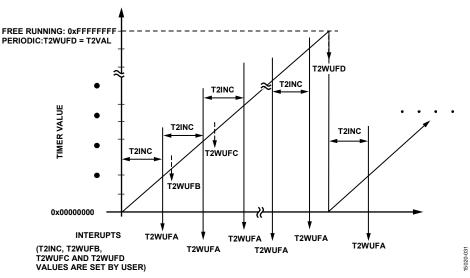

| I <sup>2</sup> C Operation105               | Wake-Up Timer152                                  |

| I <sup>2</sup> C Operating Modes107         | Wake-Up Timer Features152                         |

| I <sup>2</sup> C Memory Mapped Registers115 | Wake-Up Timer Block Diagram152                    |

| Serial Peripheral Interfaces                | Wake-Up Timer Overview152                         |

| SPI Features125                             | Wake-Up Timer Operation152                        |

| SPI Overview125                             | Wake-Up Timer Memory Mapped Registers154          |

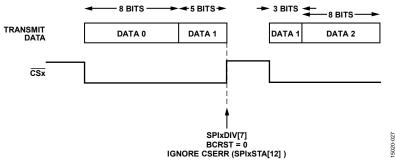

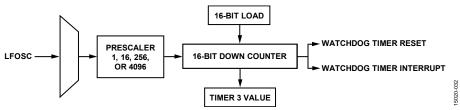

| SPI Operation125                            | Watchdog Timer159                                 |

| SPI Transfer Initiation 126                 | Watchdog Timer Features159                        |

| SPI Interrupts128                           | Watchdog Timer Block Diagram159                   |

| Wire-OR'ed Mode (WOM)129                    | Watchdog Timer Overview159                        |

| CSERR Condition 129                         | Watchdog Timer Operation159                       |

| SPI DMA129                                  | Watchdog Timer Memory Mapped Registers160         |

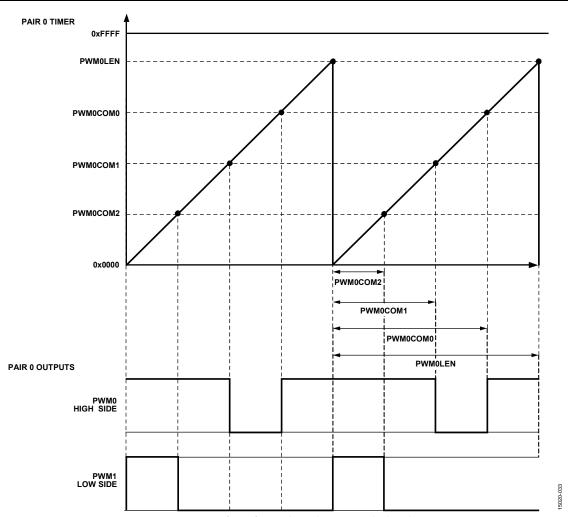

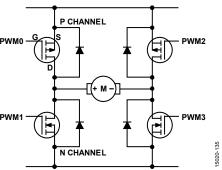

| SPI and Power-Down Modes131                 | PWM162                                            |

| SPI Memory Mapped Registers131              | PWM Features162                                   |

| UART Serial Interface                       | PWM Overview162                                   |

| UART Features                               | PWM Operation162                                  |

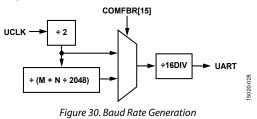

| UART Overview137                            | PWM Interrupt Generation166                       |

| UART Operation137                           | PWM Memory Mapped Registers166                    |

| Programmed I/O Mode137                      | Power Supply Support Circuits169                  |

| Enable/Disable Bit138                       | Power Supply Support Circuits Features169         |

| Interrupts138                               | Hardware Design Considerations170                 |

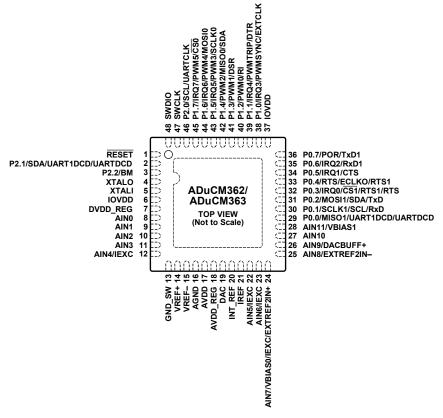

| Buffer Requirements138                      | Pin Configuration and Function Descriptions170    |

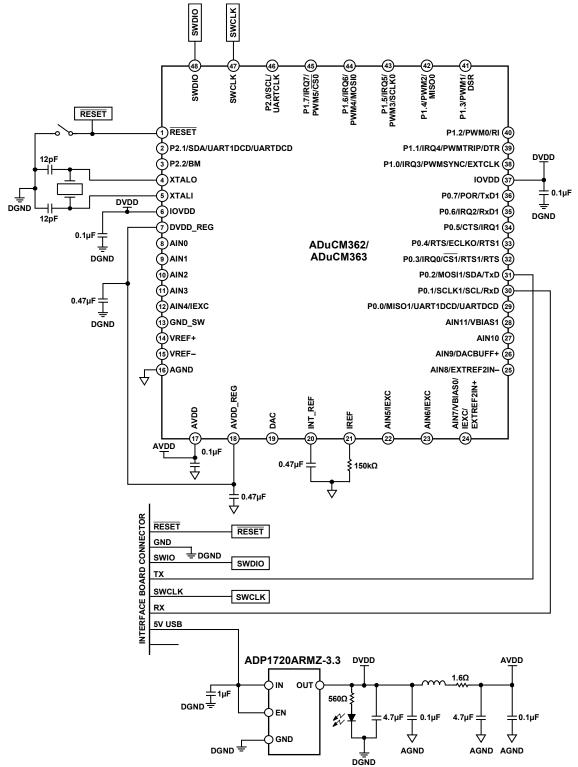

| DMA Mode138                                 | Typical System Configuration173                   |

| UART Memory Mapped Registers140             |                                                   |

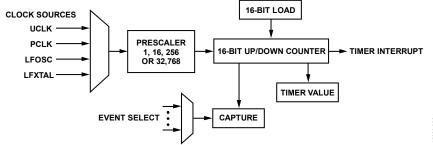

| General-Purpose Timers                      | Related Links175                                  |

| General-Purpose Timers Features 146         | 6                                                 |

| General-Purpose Timers Block Diagram 146    |                                                   |

### **REVISION HISTORY**

10/2016—Revision 0: Initial Version

# USING THE ADuCM362/ADuCM363 HARDWARE USER GUIDE

#### **NUMBER NOTATIONS**

#### **Table 1. Number Notations**

| Notation | Description                                                                                                        |

|----------|--------------------------------------------------------------------------------------------------------------------|

| Bit N    | Bits are numbered in little endian format, that is, the least significant bit of a number is referred to as Bit 0. |

| V[x:y]   | Bit field representation covering Bit x to Bit y of a value or a field (V).                                        |

| 0xNN     | Hexadecimal (Base 16) numbers are preceded by the prefix 0x.                                                       |

| 0bNN     | Binary (Base 2) numbers are preceded by the prefix 0b'.                                                            |

| NN       | Decimal (Base 10) are represented using no additional prefixes or suffixes.                                        |

#### **REGISTER ACCESS CONVENTIONS**

#### **Table 2. Register Access Conventions**

| Access | Description                                                                               |

|--------|-------------------------------------------------------------------------------------------|

| RW     | Memory location has read and write access.                                                |

| R      | Memory location is read access only. A read always returns 0, unless otherwise specified. |

| W      | Memory location is write access only.                                                     |

#### **ACRONYMS AND ABBREVIATIONS**

#### Table 3. Acronyms and Abbreviations

| Table 3. Acronyms and Abbreviations |                                                |  |

|-------------------------------------|------------------------------------------------|--|

| Acronym/Abbreviation                | Description                                    |  |

| Σ-Δ                                 | Sigma delta                                    |  |

| ADC                                 | Analog-to-digital converter                    |  |

| AF                                  | Averaging factor                               |  |

| AFE                                 | Analog front end                               |  |

| ARM                                 | Advanced RISC machine                          |  |

| CD                                  | Clock divider                                  |  |

| DMA                                 | Direct memory access                           |  |

| DSB                                 | Data synchronization barrier                   |  |

| FSE                                 | Full-scale error: gain error plus offset error |  |

| JTAG                                | Joint test action group                        |  |

| LSB                                 | Least significant byte/bit                     |  |

| MMR                                 | Memory mapped register                         |  |

| MSB                                 | Most significant byte/bit                      |  |

| NMI                                 | Nonmaskable interrupt                          |  |

| NVIC                                | Nested vectored interrupt controller           |  |

| PGA                                 | Programmable gain amplifier                    |  |

| PMU                                 | Power management unit                          |  |

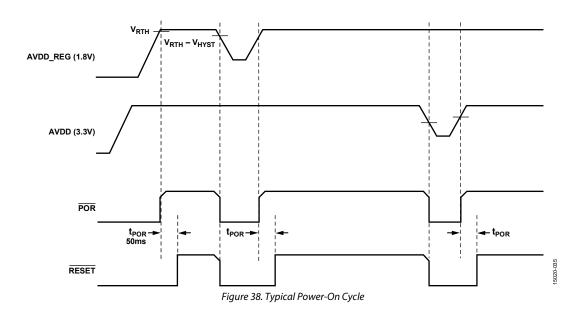

| POR                                 | Power-on reset                                 |  |

| PSM                                 | Power supply monitor                           |  |

| PWM                                 | Pulse-width modulator                          |  |

| RMS                                 | Root mean square                               |  |

| Rx                                  | Receive                                        |  |

| SF                                  | Sinc3/sinc4 filter                             |  |

| SIL                                 | Safety integrity level                         |  |

| SPI                                 | Serial peripheral interface                    |  |

| Tx                                  | Transmit                                       |  |

| UART                                | Universal asynchronous transmitter             |  |

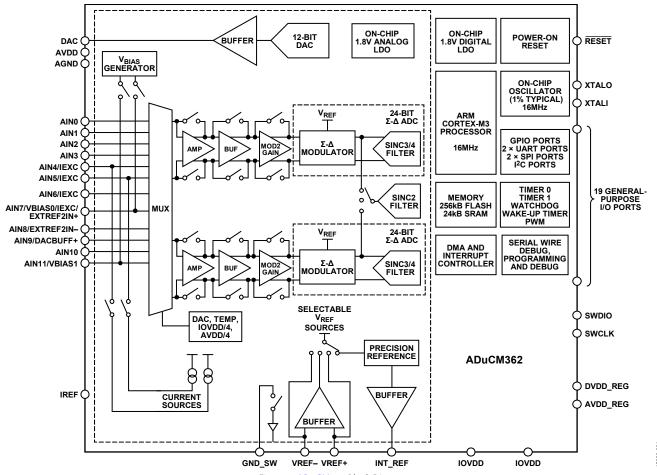

### INTRODUCTION TO THE ADuCM362/ADuCM363

The ADuCM362 is a fully integrated, 4 kSPS, 24-bit data acquisition system incorporating dual, high performance, multichannel sigmadelta ( $\Sigma$ - $\Delta$ ) analog-to-digital converters (ADCs), 32-bit ARM Cortex-M3\* processor, and Flash/EE memory on a single chip. The device is designed for direct interfacing to external precision sensors in both wired and battery-powered applications.

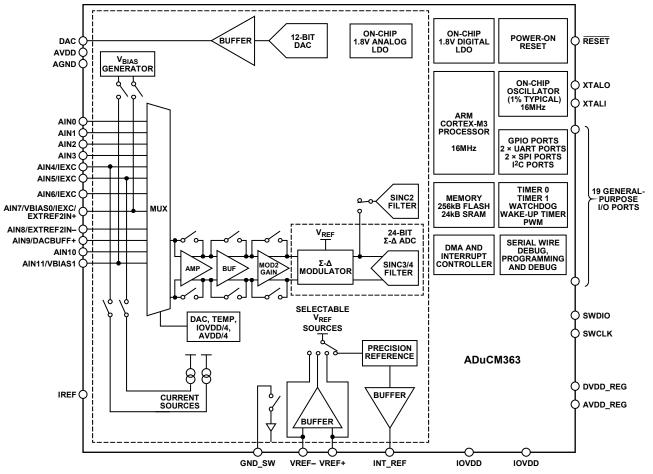

The ADuCM363 contains all the features of the ADuCM362 except ADC0. ADuCM363 only has one ADC, ADC1.

The device contains an on-chip 32 kHz oscillator and an internal 16 MHz high frequency oscillator. This clock is routed through a programmable clock divider from which the processor clock operating frequency is generated. The maximum clock speed is 16 MHz and is not limited by operating voltage or temperature.

The microcontroller is a low power Cortex-M3 processor from ARM. It is a 32-bit RISC machine, offering up to 20 MIPS peak performance. The Cortex-M3 processor incorporates a flexible 11-channel DMA controller supporting the following: 2 SPI, 2 UART, ADC and DAC. There are 256 kB of nonvolatile Flash/EE and 24 kB of SRAM integrated on chip.

The analog subsystem consists of dual ADCs, each connected to a flexible input multiplexer. Both ADCs can operate in fully differential and single-ended modes. Other on-chip ADC features include dual programmable excitation current sources, diagnostic current sources, and a bias voltage generator of AVDD\_REG/2 (900 mV) to set the common-mode voltage of an input channel. A low-side internal ground switch is provided to allow powering down of a bridge between conversions. The ADCs contain two parallel filters—a sinc3 or sinc4 in parallel with a sinc2. The sinc3 or sinc4 filter is for precision measurements. The sinc2 filter is for fast measurements and for detection of step changes in the input signal. The device also contains a low noise, low drift internal band gap reference or can be configured to accept up to two external reference sources in ratiometric measurement configurations. An option to buffer the external reference inputs is also provided on chip. A single-channel buffered voltage output DAC is also provided on chip. The ADuCM362/ADuCM363 also integrates a range of on-chip peripherals that can be configured under microcontroller software control as required in the application. These peripherals include UART, I<sup>2</sup>C, and dual SPI serial input/output (I/O) communication controllers, 19-pin GPIO ports, two general-purpose timers, wake-up timer, and system watchdog timer. A 16-bit PWM with six output channels is also provided.

The ADuCM362/ADuCM363 is specifically designed to operate in battery-powered applications where low power operation is critical. The microcontroller can be configured in a normal operating mode that consumes 290  $\mu$ A/MHz (including flash/SRAM  $I_{DD}$ ), resulting in an overall system current consumption of 1 mA when all peripherals are active.

The device can also be configured in a number of low power operating modes under direct program control, including hibernate mode (internal wake-up timer active), which consumes only  $4\,\mu A$ . In hibernate mode, peripherals, such as external interrupts or the internal wake-up timer, can wake up the device, thereby allowing the device to operate in an ultralow power operating mode while still responding to asynchronous external or periodic events.

On-chip factory firmware supports in-circuit serial download via a serial wire interface (2-pin JTAG system) and UART while nonintrusive emulation is also supported via the serial wire interface. These features are incorporated into a low cost QuickStart<sup>™</sup> development system supporting this precision analog microcontroller family.

The device operates from an external 1.8 V to 3.6 V voltage supply and is specified over an industrial temperature range of -40°C to +125°C.

Figure 2. ADuCM363 Block Diagram

#### MAIN FEATURES OF ADUCM362/ADUCM363

#### Analog I/O

- Ultrahigh precision, multichannel, dual 24-bit ADCs

- Single-ended and fully differential inputs

- Independently programmable ADC output rate (3.5 Hz to 3.906 kHz)

- Simultaneous 50 Hz/60 Hz rejection:

- 50 SPS continuous conversion mode

- 16.67 SPS single conversion mode

- Flexible input multiplexer for input channel selection to both ADCs

- ADC0 and ADC1 (24-bit) ADC channel

- 6 differential or 11 single-ended input channels

- 4 internal channels for monitoring DAC, temperature sensor, IOVDD, and AVDD (ADC1 only)

- Programmable gain (1 to 128)

- Selectable input range (see the ADuCM362/ADuCM363 data sheet for more details)

- RMS noise (see ADuCM362/ADuCM363 data sheet for more details)

- Programmable sensor excitation current sources

- $10~\mu A/50~\mu A/100~\mu A/150~\mu A/200~\mu A/250~\mu A/300~\mu A/400~\mu A/450~\mu A/500~\mu A/600~\mu A/750~\mu A/800~\mu A$  and 1 mA current source options

- On-chip precision voltage reference (see the ADuCM362/ADuCM363 data sheet for more details)

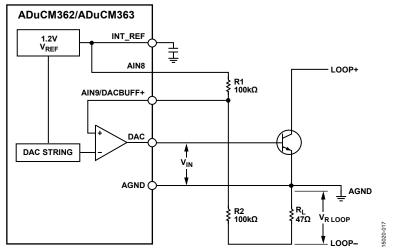

#### Single 12-Bit Voltage Output DAC

- Voltage output DAC

- Can also be configured for an NPN-transistor driver mode and interpolation mode

#### Microcontroller

- ARM Cortex-M3 32-bit processor

- Serial wire download and debug

- Internal watch crystal for wake-up timer

- 16 MHz oscillator with 8-way programmable divider

#### **Power**

- Operates directly from a 3.0 V battery

- Supply range: 1.8 V to 3.6 V

- Flexible operating modes for low power applications

- Power consumption:

- Processor active mode: core consumes 290 μA/MHz

- Active mode: 1 mA (all peripherals active) processor operating at 500 kHz

- Power-down mode: 4 µA (wake-up timer active)

#### **On-Chip Peripherals**

- UART, I<sup>2</sup>C, and two SPI serial I/O communication controllers

- 19-pin GPIO port

- Two general-purpose timers

- Wake-up timer

- Watchdog timer

- 16-bit PWM controller

- Multichannel DMA and interrupt controller

#### **Packages and Temperature Range**

• 48-lead LFCSP (7 mm × 7 mm) package -40°C to +125°C

#### **Tools**

- Low cost QuickStart development system

- Third-party compiler and emulator tool support

#### **Applications**

- Industrial automation and process control

- Intelligent, precision sensing systems

- 4 mA to 20 mA loop powered smart sensor systems

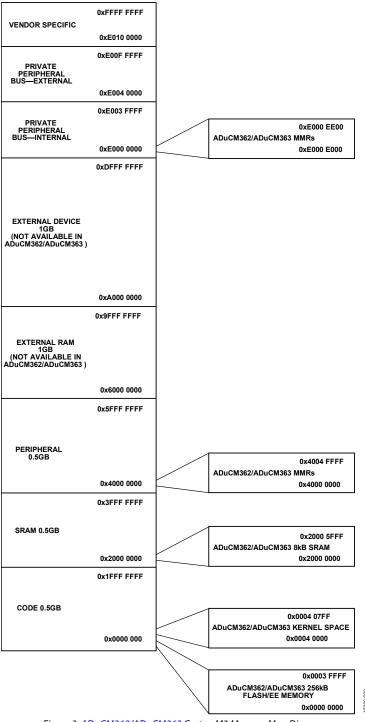

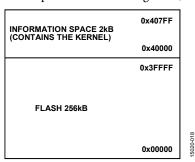

#### **MEMORY ORGANIZATION**

The ADuCM362/ADuCM363 memory organization is described in this section.

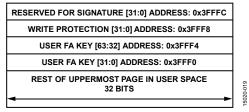

Three separate blocks of memory are accessible to the user:

- 24 kB of SRAM from 0x20000000 to 0x20005FFF

- 256 kB of on-chip Flash/EE memory available to the user from 0x00000 to 0x3FFFF

- An additional 2 kB reserved for the kernel space from 0x40000 to 0x407FF

These blocks are mapped according to the Cortex-M3 memory map as shown in Figure 3. All on-chip peripherals are accessed via memory mapped registers, situated in the bit band region.

Figure 3. ADuCM362/ADuCM363 Cortex-M3 Memory Map Diagram Rev. 0 | Page 8 of 175

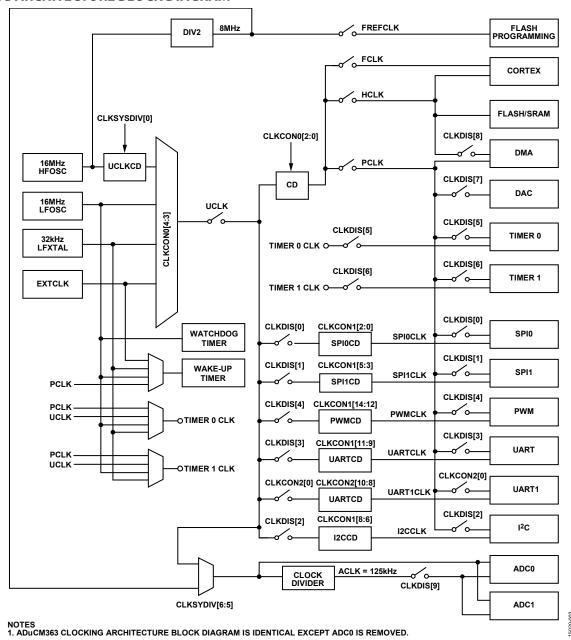

# **CLOCKING ARCHITECTURE**

#### **CLOCKING ARCHITECTURE FEATURES**

The ADuCM362/ADuCM363 integrates two on-chip oscillators and circuitry for an external crystal:

- LFOSC is a 32 kHz low power internal oscillator, used in low power modes.

- HFOSC is a 16 MHz internal oscillator that is used in active mode.

- LFXTAL is a 32 kHz external crystal.

- Power saving clock mechanism; enable and disable per peripheral.

#### **CLOCKING ARCHITECTURE BLOCK DIAGRAM**

Figure 4. ADuCM362 Clocking Architecture Block Diagram (the ADuCM363 Clocking Architecture Block Diagram is Identical, Except ADC0 Is Removed)

#### **CLOCKING ARCHITECTURE OVERVIEW**

Three of the clock sources—LFOSC, HFOSC, and LFXTAL—can be used as system clocks. An external clock on P1.0 can also be used for test purposes.

Internally, the system clock is divided into five clocks:

- FCLK for the cortex processor

- UCLK system clock

- HCLK for the flash, SRAM, DMA

- ACLK for the analog front end and ADC clock

- PCLK for the other peripherals

Figure 4 shows all the clocks available and includes clock gates for power management. For more information about the clock gates, see the Power Management Unit section.

#### **CLOCKING ARCHITECTURE OPERATION**

At power-up, the processor executes from the 16 MHz internal oscillator divided down to 1 MHz. User code can select the clock source for the system clock and can divide the clock by a factor of 2<sup>CD</sup>, where CD is the clock divider bits (CLKCON0[2:0]). Dividing the clock this way allows slower code execution and reduced power consumption.

P1.0 must be configured first as a clock input before the clock source is switched in the clock control register.

#### Memory

- 256 kB Flash/EE memory, 24 kB SRAM

- 10000 cycle Flash/EE endurance

- 10 year Flash/EE retention

- In-circuit download via serial wire and UART

#### **CLOCKING ARCHITECTURE MEMORY MAPPED REGISTERS**

Table 4. Clock Control Memory Mapped Registers Address Table

| Address    | Name      | Description                                | Access | Default |

|------------|-----------|--------------------------------------------|--------|---------|

| 0x40002000 | CLKCON0   | System Clocks Control Register 0           | RW     | 0x0001  |

| 0x40002004 | CLKCON1   | System Clocks Control Register 1           | RW     | 0xFFFF  |

| 0x4000202C | CLKDIS    | System clock to peripherals enable/disable | RW     | 0x0DFF  |

| 0x4000203C | CLKCON2   | System Clocks Control Register 2           | RW     | 0x7F07  |

| 0x40002410 | XOSCCON   | Crystal oscillator control register        | RW     | 0x0000  |

| 0x40002444 | CLKSYSDIV | Clocking architecture divide register      | RW     | 0x0063  |

UG-1048

# ADuCM362/ADuCM363 Hardware Reference Manual

#### **Clocking Architecture Control Register 0**

Address: 0x40002000, Reset: 0x0001, Name: CLKCON0

Table 5. CLKCON0 Register Bit Descriptions

| Bits   | Name     | Description                                                       |  |

|--------|----------|-------------------------------------------------------------------|--|

| [15:8] | Reserved | Reserved                                                          |  |

| [7:5]  | CLKOUT   | Clock out multiplexer selection bits (use for test purposes only) |  |

|        |          | 000: UCLK (default)                                               |  |

|        |          | 001: UCLK                                                         |  |

|        |          | 010: PCLK                                                         |  |

|        |          | 011: reserved                                                     |  |

|        |          | 100: reserved                                                     |  |

|        |          | 101: HFOSC                                                        |  |

|        |          | 110: LFOSC                                                        |  |

|        |          | 111: LFXTAL                                                       |  |

| [4:3]  | CLKMUX   | Clock in multiplexer selection bits                               |  |

|        |          | 00: HFOSC (default)                                               |  |

|        |          | 01: LFXTAL                                                        |  |

|        |          | 10: LFOSC                                                         |  |

|        |          | 11: EXTCLK                                                        |  |

| [2:0]  | CD       | Clock divide bits <sup>1</sup>                                    |  |

|        |          | 000: DIV1: UCLK/1                                                 |  |

|        |          | 001: DIV2: UCLK/2 (default)                                       |  |

|        |          | 010: DIV4: UCLK/4                                                 |  |

|        |          | 011: DIV8: UCLK/8                                                 |  |

|        |          | 100: DIV16: UCLK/16                                               |  |

|        |          | 101: DIV32: UCLK/32                                               |  |

|        |          | 110: DIV64: UCLK/64                                               |  |

|        |          | 111: DIV128: UCLK/128                                             |  |

$<sup>^{\</sup>rm 1}$  UCLK is the 16 MHz system clock divided by the CLKSYSDIV (Bits[1:0]) bit setting.

#### **Clocking Architecture Control Register 1**

Address: 0x40002004, Reset: 0xFFFF, Name: CLKCON11

Table 6. CLKCON1 Register Bit Descriptions

| Bits    | Name     | Description                                                                       |

|---------|----------|-----------------------------------------------------------------------------------|

| 15      | Reserved | Reserved                                                                          |

| [14:12] | PWMCD    | Clock divide bits for PWM system clock <sup>2</sup>                               |

|         |          | 000: UCLK/1 = 16 MHz                                                              |

|         |          | 001: UCLK/2 = 8 MHz                                                               |

|         |          | 010: UCLK/4 = 4 MHz                                                               |

|         |          | 011: UCLK/8 = 2 MHz                                                               |

|         |          | 100: UCLK/16 = 1 MHz                                                              |

|         |          | 101: UCLK/32 = 500 kHz                                                            |

|         |          | 110: UCLK/64 = 250 kHz                                                            |

|         |          | 111: UCLK/128 = 125 kHz                                                           |

| [11:9]  | UARTCD   | Clock divide bits for UART system clock <sup>2</sup>                              |

|         |          | 000: UCLK/1 = 16 MHz                                                              |

|         |          | 001: UCLK/2 = 8 MHz                                                               |

|         |          | 010: UCLK/4 = 4 MHz                                                               |

|         |          | 011: UCLK/8 = 2 MHz                                                               |

|         |          | 100: UCLK/16 = 1 MHz                                                              |

|         |          | 101: UCLK/32 = 500 kHz                                                            |

|         |          | 110: UCLK/64 = 250 kHz                                                            |

|         |          | 111: UCLK/128 = 125 kHz                                                           |

| [8:6]   | I2CCD    | Clock divide bits for I <sup>2</sup> C system clock <sup>2</sup>                  |

|         |          | 000: UCLK/1 = 16 MHz                                                              |

|         |          | 001: UCLK/2 = 8 MHz (minimum value to support 400 kHz $I^2$ C baud rate)          |

|         |          | 010: UCLK/4 = 4 MHz                                                               |

|         |          | 011: UCLK/8 = 2 MHz (minimum value to support 100 kHz I <sup>2</sup> C baud rate) |

|         |          | 100: UCLK/16 = 1 MHz                                                              |

|         |          | 101: UCLK/32 = 500 kHz                                                            |

|         |          | 110: UCLK/64 = 250 kHz                                                            |

|         |          | 111: UCLK/128 = 125 kHz                                                           |

| [5:3]   | SPI1CD   | Clock divide bits for SPI1 system clock <sup>2</sup>                              |

|         |          | 000: UCLK/1 = 16 MHz                                                              |

|         |          | 001: UCLK/2 = 8 MHz                                                               |

|         |          | 010: UCLK/4 = 4 MHz                                                               |

|         |          | 011: UCLK/8 = 2 MHz                                                               |

|         |          | 100: UCLK/16 = 1 MHz                                                              |

|         |          | 101: UCLK/32 = 500 kHz                                                            |

|         |          | 110: UCLK/64 = 250 kHz                                                            |

|         |          | 111: UCLK/128 = 125 kHz                                                           |

| [2:0]   | SPI0CD   | Clock divide bits for SPI0 system clock <sup>2</sup>                              |

|         |          | 000: UCLK/1 = 16 MHz                                                              |

|         |          | 001: UCLK/2 = 8 MHz                                                               |

|         |          | 010: UCLK/4 = 4 MHz                                                               |

|         |          | 011: UCLK/8 = 2 MHz                                                               |

|         |          | 100: UCLK/16 = 1 MHz                                                              |

|         |          | 101: UCLK/32 = 500 kHz                                                            |

|         |          | 110: UCLK/64 = 250 kHz                                                            |

|         |          | 111: UCLK/128 = 125 kHz                                                           |

$<sup>^{1}</sup>$  Peripheral clock must be greater than or equal to the FCLK. FCLK is set by CLKCON0[2:0].  $^{2}$  Calculations are for UCLK = 16 MHz with CLKSYSDIV[1:0] set to 0. An additional factor must be taken into account if CLKSYSDIV[1:0] is not set to 0.

UG-1048

# ADuCM362/ADuCM363 Hardware Reference Manual

#### Clocking Architecture Disable Register

Address: 0x4000202C, Reset: 0x0DFF, Name: CLKDIS

**Table 7. CLKDIS Register Bit Descriptions**

| Bits    | Name       | Description                                    |

|---------|------------|------------------------------------------------|

| [15:12] | Reserved   | These bits are reserved and must be written 0. |

| [11:10] | Reserved   | These bits are reserved and must be written 1. |

| 9       | DISADCCLK  | 0: enable ADC system clock (default).          |

|         |            | 1: disable ADC system clock.                   |

| 8       | DISDMACLK  | 0: enable DMA system clock.                    |

|         |            | 1: disable DMA system clock.                   |

| 7       | DISDACCLK  | 0: enable DAC system clock.                    |

|         |            | 1: disable DAC system clock.                   |

| 6       | DIST1CLK   | 0: enable Timer 1 system clock.                |

|         |            | 1: disable Timer 1 system clock.               |

| 5       | DIST0CLK   | 0: enable Timer 0 system clock.                |

|         |            | 1: disable Timer 0 system clock.               |

| 4       | DISPWMCLK  | 0: enable PWM system clock.                    |

|         |            | 1: disable PWM system clock.                   |

| 3       | DISUARTCLK | 0: enable UART system clock.                   |

|         |            | 1: disable UART clock.                         |

| 2       | DISI2CCLK  | 0: enable I <sup>2</sup> C system clock.       |

|         |            | 1: disable I <sup>2</sup> C system clock.      |

| 1       | DISSPI1CLK | 0: enable SPI1 system clock.                   |

|         |            | 1: disable SPI1 system clock.                  |

| 0       | DISSPI0CLK | 0: enable SPI0 system clock.                   |

|         |            | 1: disable SPI0 system clock.                  |

#### **Clocking Architecture Control Register 2**

Address: 0x4000203C, Reset: 0x7F07, Name: CLKCON2

Table 8. CLKCON2 Register Bit Descriptions

| Bits    | Name        | Description                                          |

|---------|-------------|------------------------------------------------------|

| 15      | Reserved    | These bits are reserved and must be written 0.       |

| 14      | DACCD       | Clock divide bits for DAC system clock. <sup>1</sup> |

|         |             | 0: UCLK/8 = 2 MHz.                                   |

|         |             | 1: UCLK/16 = 1 MHz.                                  |

| [13:11] | Reserved    | These bits are reserved and must be written 1.       |

| [10:8]  | UART1CD     | Clock divide bits for UART1 system clock.1           |

|         |             | 000: UCLK/1 = 16 MHz.                                |

|         |             | 001: UCLK/2 = 8 MHz.                                 |

|         |             | 010: $UCLK/4 = 4 MHz$ .                              |

|         |             | 011: UCLK/8 = 2 MHz.                                 |

|         |             | 100: UCLK/16 = 1 MHz.                                |

|         |             | 101: UCLK/32 = 500 kHz.                              |

|         |             | 110: UCLK/64 = 250 kHz.                              |

|         |             | 111: UCLK/128 = 125 kHz (default).                   |

| [7:3]   | Reserved    | These bits are reserved and must be written 0.       |

| [2:1]   | Reserved    | These bits are reserved and must be written 1.       |

| 0       | DISUART1CLK | 0: enable UART1 clock.                               |

|         |             | 1: disable UART1 clock (default).                    |

¹ Calculations are for UCLK = 16 MHz with CLKSYSDIV[1:0] set to 0. An additional factor must be taken into account if CLKSYSDIV[1:0] is not set to 0.

#### **External Crystal Oscillator Control Register**

Address: 0x40002410, Reset: 0x0000, Name: XOSCCON

**Table 9. XOSCCON Register Bit Descriptions**

| Bits  | Name     | Description                                     |

|-------|----------|-------------------------------------------------|

| [7:3] | Reserved | These bits are reserved; write 0 to these bits. |

| 2     | DIV2     | Divide-by-2 enable bit.                         |

|       |          | 0: disable the clock divider.                   |

|       |          | 1: enable the clock divider.                    |

| 1     | Reserved | This bit is reserved; write 0 to these bits.    |

| 0     | ENABLE   | Crystal oscillator circuit enable.              |

|       |          | 0: disable the oscillator circuitry.            |

|       |          | 1: enable the oscillator circuitry.             |

UG-1048

# ADuCM362/ADuCM363 Hardware Reference Manual

### Clocking Architecture Divide Register

Address: 0x40002444, Reset: 0x0063, Name: CLKSYSDIV

#### Table 10. CLKSYSDIV Register Bit Descriptions

| Bits   | Name     | Description                                                                        |

|--------|----------|------------------------------------------------------------------------------------|

| [15:7] | Reserved | These bits are reserved and must be written 0.                                     |

| [6:5]  | ADCCLK   | Selects the clock source for the ADC                                               |

|        |          | 00: the ADC is clocked from UCLK. This setting can only be used if UCLK is 16 MHz. |

|        |          | 01: reserved.                                                                      |

|        |          | 10: the ADC is clocked from UCLK. This setting can only be used if UCLK is 8 MHz.  |

|        |          | 11: the ADC is clocked from an 8 MHz clock (default).                              |

| [3:2]  | Reserved | These bits are reserved and must be written 0.                                     |

| [1:0]  | UCLKCD   | Clock divide bits for UCLK system clock.                                           |

|        |          | 00: UCLK = 16 MHz.                                                                 |

|        |          | 01: UCLK = 8 MHz.                                                                  |

|        |          | 10: UCLK = 4 MHz.                                                                  |

|        |          | 11: UCLK = 2 MHz.                                                                  |

### **POWER MANAGEMENT UNIT**

#### **POWER MANAGEMENT UNIT FEATURES**

The power management unit (PMU) controls the different power modes of the ADuCM362/ADuCM363.

Six power modes are available as follows:

- Active

- MCUHALT

- PERHALT

- SYSHALT

- TOTALHALT

- Hibernate

#### **POWER MANAGEMENT UNIT OVERVIEW**

The PMU controls the power modes of the ADuCM362/ADuCM363.

The Cortex-M3 sleep modes are linked to the PMU modes and are described in this section. The PMU is in the always on section. Each mode gives a power reduction benefit with a corresponding reduction in functionality. The most restrictive mode gives a power-down figure of  $\sim$ 4  $\mu$ A, and the least restrictive mode gives a power-down figure that is dependent on the CD clock rate chosen by the user,  $\sim$ 290  $\mu$ A/MHz.

All current values are available in the ADuCM362/ADuCM363 data sheet.

**Table 11. Power Modes Summary**

| Mode | Name      | Description                                                      | Estimated Current <sup>1</sup><br>CLKSYSDIV[1:0] = 0 | Estimated Current<br>CLKSYSDIV[1:0] = 1 | Wake-Up Time            |

|------|-----------|------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------|-------------------------|

| 0    | Active    | Full active mode.                                                | 250 μA + 290 μA/MHz                                  | 145 μA + 145 μA/MHz                     |                         |

| 1    | MCUHALT   | Gate HCLK when Cortex-M3 is also in sleep modes.                 | 435 μA + 50 μA/MHz                                   | 355 μA + 50 μA/MHz                      | 3 × FCLK to<br>5 × FCLK |

| 2    | PERHALT   | Gate PCLK when Cortex-M3 also is in sleep modes.                 | 425 μA + 60 μA/MHz                                   | 345 μA + 60 μA/MHz                      | 3 × FCLK to<br>5 × FCLK |

| 3    | SYSHALT   | Gate both HCLK, ACLK, and PCLK when Cortex-M3 is in sleep modes. | 420 μA + 16 μA/MHz                                   | 345 μA + 16 μA/MHz                      | 3 × FCLK to<br>5 × FCLK |

| 4    | TOTALHALT | Gate FCLK when Cortex-M3 is in deep sleep mode.                  | ~4 µA                                                | ~4 µA                                   | 30.8 μs                 |

| 5    | Hibernate | Turns all digital blocks off except always on blocks.            | ~4 µA                                                | ~4 µA                                   | 30.8 μs                 |

<sup>1</sup> Estimated current = static current + dynamic current, where dynamic current is frequency. The values given are typical values at TA = 25°C.

#### POWER MANAGEMENT UNIT OPERATION

The debug tools can prevent the Cortex-M3 from fully entering its power saving modes by setting bits in the debug logic. Only a power-on reset resets the debug logic. Therefore, power cycle the device after using serial wire debug with application code containing the WFI instruction.

#### Power Mode: Active Mode, Mode 0

The system is fully active. Memories and all user enabled peripherals are clocked, and the Cortex-M3 processor is executing instructions. The Cortex-M3 processor manages its internal clocks and can be in a partial clock gated state. This clock gating affects only the internal Cortex-M3 processing core. Automatic clock gating is used on all blocks and is transparent to the user. User code can use a WFI command to put the Cortex-M3 processor into sleep mode; it is independent of the power mode settings of the PMU.

When the ADuCM362/ADuCM363 wake up from any of the low power mode, the devices return to Mode 0.

#### Power Mode: MCUHALT Mode, Mode 1

The system gates HCLK at an early stage, after the Cortex-M3 processor enters sleep mode. The HCLK is the clock to the SRAM, flash, and DMA blocks. The gating of this clock stops all these peripherals. The Cortex-M3 processor FCLK is active, and the device wakes up using the NVIC. If ADC0, ADC1, or sinc2 DMA channels are enabled in the DMAENSET register, the clock remains active to the DMA block and the SRAM.

#### Power Mode: PERHALT Mode, Mode 2

The system gates PCLK at an early stage, after the Cortex-M3 processor enters sleep mode. The PCLK is the clock to user peripherals. The gating of this clock stops all clocks to these peripherals. The Cortex-M3 processor FCLK is active and the device wakes up using the NVIC. If ADC0, ADC1, or sinc2 DMA channels are enabled in the DAMENSET register, the clock remains active to the DMA block and the SRAM.

#### Power Mode: SYSHALT Mode, Mode 3

The system gates HCLK and PCLK at an early stage, after the Cortex-M3 processor enters sleep mode. The Cortex-M3 processor FCLK is active and the device wakes up using the NVIC.

#### Power Mode: TOTALHALT Mode, Mode 4

The system gates FCLK, HCLK, and PCLK at an early stage, after the Cortex-M3 processor enters deep sleep mode. The FCLK is the free running clock of the Cortex-M3 processor. The gating of FCLK, HCLK, and PCLK clocks stops some of the NVIC functionality. The Cortex-M3 processor FCLK is, therefore, stopped and only the peripherals listed in Table 56 can wake up the Cortex-M3 processor. The low power LDO is turned on and the high power LDO is turned off automatically when entering Mode 4.

#### Power Mode: Hibernate Mode, Mode 5

The system gates power to the digital core. All states are retained during this power gating, which appears to the user as a clock gating of FCLK, HCLK, and PCLK at an early stage, after the Cortex-M3 processor enters deep sleep mode; however, the leakage current is lower and the response time is different (that is, the device is slower to come up). The Cortex-M3 processor FCLK is, therefore, stopped and only the peripherals listed in Table 56 can wake up the Cortex-M3 processor.

The low power LDO enabled in Power Mode 4 and Power Mode 5 is only capable of sourcing 100  $\mu$ A typically. Therefore, users must be careful that no high frequency clock signals (that is, signals greater than 1 MHz) are provided on digital inputs because such signals can cause internal circuits to consume power that exceeds this 100  $\mu$ A limit. Therefore, Power Mode 4 and Power Mode 5 are not supported when an external clock is present on P1.0. These modes are supported, however, when digital pins are sourcing current as digital outputs because this current is sourced from the IOVDD supply and not the low power LDO.

If a power mode in the Power Mode 1 to Power Mode 5 range is entered when the processor is in an interrupt handler, the power-down mode can be exited only by a reset or a higher priority interrupt source.

#### POWER MANAGEMENT UNIT MEMORY MAPPED REGISTERS

The power modes are controlled by a single register based in the section that is always on at Address 0x40002400.

Table 12. System Clocks Memory Mapped Register Address (Base Address: 0x40002400)

| Offset | Name   | Description               | Access | Default        |

|--------|--------|---------------------------|--------|----------------|

| 0x0000 | PWRMOD | Power modes register      | RW     | 0x00           |

| 0x0004 | PWRKEY | Key protection for PWRMOD | RW     | Not applicable |

#### **Power Modes Control Register**

Address: 0x40002400, Reset: 0x0000, Name: PWRMOD

Table 13. PWRMOD Register Bit Descriptions

| Bits  | Name     | Description                                                                                                                              |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| [7:3] | Reserved | Reserved. Write these bits 0 by user code.                                                                                               |

| [2:0] | MOD      | Power modes control bits. Selects the power mode to enter. When read, these bits contain the last power mode value entered by user code. |

|       |          | 000: full active.                                                                                                                        |

|       |          | 001: MCUHALT.                                                                                                                            |

|       |          | 010: PERHALT.                                                                                                                            |

|       |          | 011: SYSHALT.                                                                                                                            |

|       |          | 100: TOTALHALT.                                                                                                                          |

|       |          | 101: hibernate.                                                                                                                          |

|       |          | Other: reserved.                                                                                                                         |

To place the cortex in deep sleep mode when the device is in Mode 4 or Mode 5, the Cortex-M3 processor system control register (Address 0xE000ED10) must be configured to 1 in Bit 2 (SCR[2]).

#### **Power Modes Key Register**

Address: 0x40002400, Reset: Not Applicable, Name: PWRKEY

#### **Table 14. PWRKEY Register Bit Descriptions**

| Bits   | Name  | Description                                                                                                                                                                                                                                                                                                                     |

|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15:0] | VALUE | Power control key register. The PWRMOD register is key protected. Two writes to the key are necessary to change the value in the PWRMOD register: first write 0x4859, and then write 0xF27B. Then, write to the PWRMOD register. A write to another register before writing to PWRMOD returns the protection to the lock state. |

#### **Code Example to Enter Power Saving Modes**

```

SCB -> SCR = 0x04;

// sleepdeep mode

pADI_PWRCTL->PWRKEY = 0x4859;

// key1

pADI_PWRCTL->PWRKEY = 0xF27B;

// key2

pADI_PWRCTL->PWRMOD = 0x4;

asmwfi();

__asm void asmwfi()

nop

nop

nop

WFI

nop

nop

BX LR

}

```

### **CORTEX-M3 PROCESSOR**

#### **CORTEX-M3 PROCESSOR FEATURES**

#### **High Performance**

- 1.25 DMIPS/MHz.

- Many instructions, including multiply, are single cycle.

- Separate data and instruction buses allow simultaneous data and instruction accesses to be performed.

- Optimized for single-cycle flash usage.

#### **Low Power**

- Low standby current.

- Core implemented using advanced clock gating so that only the actively used logic consumes dynamic power.

- Power saving mode support (sleep and deep sleep modes). The design has separate clocks to allow unused parts of the processor to be stopped.

#### **Advanced Interrupt Handling**

- The nested vectored interrupt controller (NVIC) supports up to 240 interrupts. The ADuCM362/ADuCM363 supports 38 of these.

The vectored interrupt feature greatly reduces interrupt latency because there is no need for software to determine which interrupt handler to serve. In addition, there is no need to have software to set up nested interrupt support.

- The Cortex-M3 processor automatically pushes registers onto the stack at the entry interrupt and pops them back at the exit interrupt, reducing interrupt handling latency and allowing interrupt handlers to be normal C functions.

- Dynamic priority control for each interrupt.

- Latency reduction using late arrival interrupt acceptance and tail-chain interrupt entry.

- Immediate execution of a nonmaskable interrupt request for safety-critical applications.

#### **System Features**

- Support for bit-band operation and unaligned data access.

- Advanced fault handling features include various exception types and fault status registers.

#### **Debug Support**

- Serial wire debug interfaces (SW-DP).

- Flash patch and breakpoint (FPB) unit for implementing breakpoints. Limited to six active breakpoints.

- Data watchpoint and trigger (DWT) unit for implementing watchpoints, trigger resources, and system profiling. Limited to two

active watchpoints.

#### **CORTEX-M3 PROCESSOR OVERVIEW**

The ADuCM362/ADuCM363 contains an embedded ARM Cortex-M3 processor, Revision r2p0 (AT420). The ARM Cortex-M3 provides a high performance, low cost platform that meets the system requirements of minimal memory implementation, reduced pin count, and low power consumption while delivering outstanding computational performance and exceptional system response to interrupts.

#### **CORTEX-M3 PROCESSOR OPERATION**

Several Cortex-M3 components are flexible in their implementation. This section details the actual implementation of these components in the ADuCM362/ADuCM363.

#### Serial Wire Debug (SW/JTAG-DP)

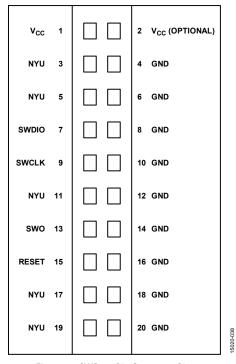

The ADuCM362/ADuCM363 only supports the serial wire interface via the SWCLK and SWDIO pins. It does not support the 5-wire JTAG interface.

#### **ROM Table**

The ADuCM362/ADuCM363 implements the default ROM table.

#### **Nested Vectored Interrupt Controller Interrupts (NVIC)**

The Cortex-M3 processor includes a nested vectored interrupt controller (NVIC), which offers several features:

- Nested interrupt support

- Vectored interrupt support

- Dynamic priority changes support

- Interrupt masking

In addition, the NVIC has a nonmaskable interrupt (NMI) input.

The NVIC is implemented on the ADuCM362/ADuCM363, and more details are available in the System Exceptions and Peripheral Interrupts section.

#### Wake-Up Interrupt Controller (WIC)

The ADuCM362/ADuCM363 has a modified WIC, which provides the lowest possible power-down current. This feature is transparent to the user, and more details are available in the Power Management Unit section.

If the device enters a power saving mode when servicing an interrupt, it can be woken up only by a higher priority interrupt source.

#### μDMA

The ADuCM362/ADuCM363 implements the ARM μDMA. More details are available in the DMA Controller section.

#### **RELATED DOCUMENTS**

- Cortex-M3 Revision r2p0 Technical Reference Manual (DDI0337)

- Cortex-M3 Errata Notice: Cortex-M3/Cortex-M3 with ETM (AT420/AT425)

- ARMv7-M Architecture Reference Manual (DDI0403)

- ARMv7-M Architecture Reference Manual Errata markup

- ARM Debug Interface v5 (IHI0031)

- PrimeCell μDMA Controller (PL230) Technical Reference Manual Revision r0p0 (DDI0417)

### **ADC CIRCUIT**

#### **ADC CIRCUIT FEATURES**

- ADuCM362: two Σ-Δ ADCs (ADC0 and ADC1)

- ADuCM363: one  $\Sigma$ - $\Delta$  ADC (ADC1)

- Six fully differential inputs

- Eleven single-ended inputs

#### **ADC CIRCUIT BLOCK DIAGRAM**

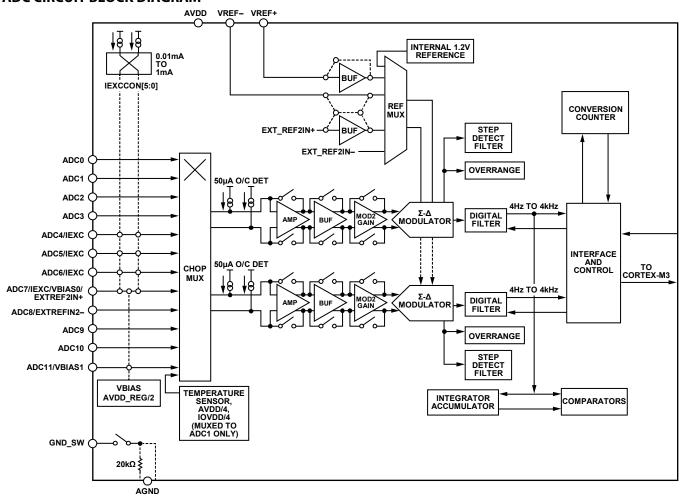

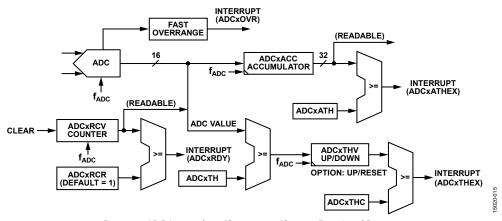

Figure 5. ADC Block Diagram

#### **ADC CIRCUIT OVERVIEW**

The ADuCM362 incorporates two independent multichannel  $\Sigma$ - $\Delta$  ADCs (ADC0 and ADC1).

The ADuCM363 incorporates one multichannel  $\Sigma$ - $\Delta$  ADC (ADC1).

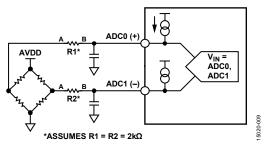

Both ADCs are connected to a common input multiplexer of six fully differential inputs or 11 single-ended inputs. The device also contains a low noise, low drift internal band gap reference. The device accepts two external reference sources and provides the option of buffering these inputs. Other on-chip ADC features include dual programmable excitation current sources, diagnostic current sources, and a bias voltage generator of AVDD\_REG/2 to set the common-mode voltage of an input channel. A low-side internal ground switch is provided that allows powering down an external sensor between conversions.

Both ADCs share the same input multiplexer. Each ADC has a separate input buffer and a low noise programmable gain amplifier (PGA) that allows small amplitude signals to be connected directly to the  $\Sigma$ - $\Delta$  modulator of each ADC. The analog input pins can be configured as fully differential input pairs or as single-ended pairs. In single-ended mode, the channel selected by the ADCCN in the ADCxCON register acts as the negative input channel reference to the ADC. The same channel can be used as a negative input for all other single-ended positive

inputs. These can be connected to ground. ADC1 also supports four internal channels: AVDD/4, IOVDD/4, temperature sensor, and DAC. The ADCs operate independently of each other, and each has its own individual Cortex-M3 processor interrupt sources and configuration register set.

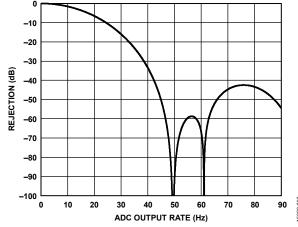

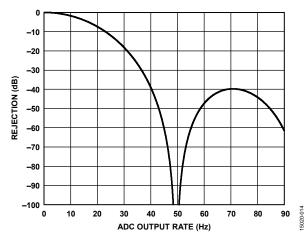

For fast processing of the ADC inputs, it is possible to select a faster sinc2 filter to operate in parallel with the normal sinc3 or sinc4 filter on either ADC0 or ADC1. This filter outputs data every 2 ms and can be read continuously. Alternatively, the sinc2 filter can be used for fast detection of step changes on an ADC input channel. In addition, for higher precision at high sampling rates (488 Hz to 4 kHz), a sinc4 filter is provided.

If an error occurs during an ADC conversion or calibration routine (for example, a missing reference), the ADCxDAT registers read full scale for the particular gain setting and ADCxSTA[4] is set to 1 for an overflow error. ADCxDAT reports negative full scale for an underflow error, and again ADCxSTA[4] is set to 1.

On the ADuCM363, ADC0 is not available.

On the ADuCM363, ADC1 is identical to ADC1 of the ADuCM362.

#### **ADC CIRCUIT OPERATION**

#### **Analog Input Channel Configuration**

Both ADCs are connected to a common input multiplexer.

The ADCCP (ADCxCON[9:5]) and ADCCN (ADCxCON[4:0]) bits of the ADC control registers configure the input signals to each ADC as follows:

- ADC0CON[9:5]: These bits select the positive input channel to ADC0. The bits can select any of the following input channels as the source: AIN0/AIN1/AIN2/AIN3/AIN4/AIN5/AIN6/AIN7/AIN8/AIN9/AIN10/AIN11 or AGND.

- ADC0CON[4:0]: These bits select the negative input channel to ADC0. The bits can select any of the following input channels as the source: AIN0/AIN1/AIN2/AIN3/AIN4/AIN5/AIN6/AIN7/AIN8/AIN9/AIN10/AIN11 or AGND.

- ADC1CON[9:5]: These bits select the positive input channel to ADC1. The bits can select any of the following input channels as the source: AIN0/AIN1/AIN2/AIN3/AIN4/AIN5/AIN6/AIN7/AIN8/AIN9/AIN10/AIN11 or any of the internal channels (that is, DAC output, temperature sensor channel, AVDD ÷ 4, or IOVDD ÷ 4).

- ADC1CON[4:0]: These bits select the negative input channel to ADC1. The bits can select any of the following input channels as the source: AIN0/AIN1/AIN2/AIN3/AIN4/AIN5/AIN6/AIN7/AIN8/AIN9/AIN10/AIN11 or any of the internal channels (that is, DAC output, temperature sensor channel, AVDD, or IOVDD).

The input channels can be buffered or unbuffered. In buffered mode, the selected input channel feeds into a high impedance input stage of the amplifier, allowing the ADC to tolerate significant source impedances and allowing direct connection to resistive type sensors, such as RTDs and strain gauges. In unbuffered mode, this input buffer is bypassed and affords a wider input voltage range. The buffer is controlled by ADCxCON[17:14].

See the specifications in the ADuCM362/ADuCM363 data sheet for further details.

The ADuCM362 supports a mode of operation in which the PGA on both ADCs can drive the ADC modulator directly regardless of the gain setting, allowing the input buffers to be bypassed and powered down. Because each positive and negative input buffer consumes typically 35  $\mu$ A, this represents an IDD saving of 140  $\mu$ A if both ADCs are enabled. The ADuCM363 also supports such a mode of operation, but on ADC1 only. The time to a first valid (fully settled) result after an input channel switch is shown in Table 17, tsettling.

#### Connecting the Same Input Channel to the Positive Input of Both ADCs (ADuCM362 Only)

The ADuCM362 has two independent ADCs and a fully flexible input multiplexer that allow the positive inputs to both ADCs to be connected to the same input channel.

Most applications separate the input channels to each ADC. However, in some cases—for example, in industrial applications—it may be desirable to measure the same input on both ADCs to improve the safety integrity level (SIL) ratings.

If the PGA is enabled (gain  $\geq$  2), the ADC output value when both ADCs are sampling the same input is different compared with when just one ADC is sampling this input. The reason for the difference is due to the change in input current when the analog input is connected to both PGAs compared with when it is connected to just one.

When measuring an input channel with both ADCs, it is recommend that separate zero-scale and full-scale calibration values be used for this condition. Generate these calibration values via the system calibration mode of the ADC.

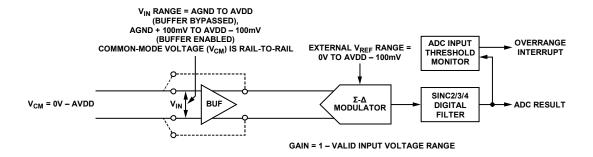

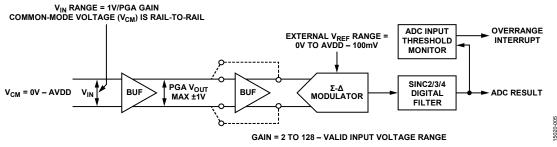

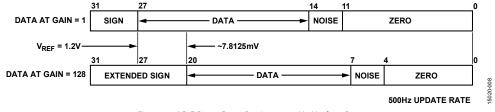

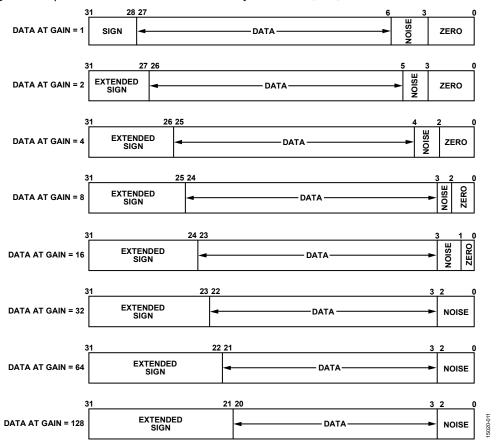

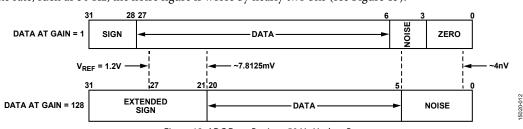

#### **PGA Gain Configuration**

Both ADCs incorporate an on-chip programmable gain amplifier (PGA). The PGA can be programmed through eight different settings, resulting in a range of 1 to 128. The gain is controlled by the ADC0MDE[7:4] and ADC1MDE[7:4] control registers. The PGA allows signals of very small amplitude to be gained up while still maintaining low noise performance. In unipolar mode (based on a 1.2 V ADC reference), the input range varies from 0 V to 1.2 V using a gain of 1 or from 0 mV to 7.8125 mV using a gain of 128. In bipolar mode, the input range changes to 0 V to  $\pm 1.2$  V with a gain of 1 and to 0 mV to  $\pm 7.8125$  mV with a gain of 128.

When a gain of 1 is selected, the PGA is not enabled. The PGA is enabled only for gains of 2, 4, 8, 16, 32, 64, and 128. When the PGA is enabled, the PGA output voltage must not exceed 1 V. Therefore, when using a gain of 4, the maximum input voltage that can be applied is ±250 mV; when using a gain of 8, the maximum input voltage that can be applied is ±125 mV. For the full list of valid input voltage ranges for all ADCs, refer to the ADuCM362/ADuCM363 data sheet. To determine if the ADC input is about to exceed the 1 V PGA output threshold, the ADC comparator can be used. The following code example shows how to set the comparator threshold to 1 V. An interrupt is asserted if the threshold is exceeded. This code is valid for all ADC0 PGA gain settings from 2 to 128.

#### **Code Example**

```

void ADC0INIT(void)

pADI\_ADC0->MSKI = 0x5;

// Enable ADC0 /rdy IRQ

+ ADCxTHEX

interrupt

pADI\_ADC0->PRO = 0x4;

// Enable threshold detection

pADI\_ADC0->TH = 0x6AA2;

// Set threshold to 1 V max PGA output

// Add rest of ADC init code after this

In the interrupt handler, add the following:

uiADCSTA = pADI_ADC0->STA;

// read ADC status register

if ((uiADCSTA & 0x4) == 0x4)

// Check for ADCOTH exceeded

condition

// 1 V threshold

ucADC0ERR = 4;

exceeded

// Disable threshold detection

pADI ADCO->MSKI &= 0xFB;

to clear this interrupt source

pADI ADC0->PRO = 0;

// Disable threshold detection

to clear this interrupt source

Optional-reenable in main loop:

// Disable threshold detection to clear this interrupt source

if (ucADC0ERR == 0x4)

{

ucadcoerr = 0;

pADI_ADC0->MSKI = 0x4;

pADI\_ADC0->PRO = 4;

```

An optional extra gain of 2 can be added in the ADC modulator; that is, a gain of 2 can be added to the output of the PGA. The 1 V PGA output limitation remains, but this extra feature results in an additional 0.5 LSB rms bits of resolution.

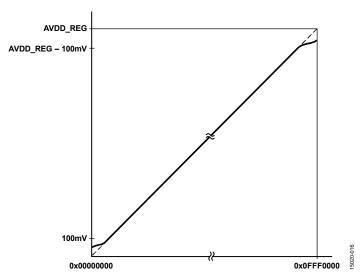

Figure 6. ADC Inputs

Table 15. Absolute Input Voltage and Common-Mode Voltage Ranges for All Gains

| Gain      | Absolute Input Voltage Range <sup>1</sup><br>(Buffers Off) | Absolute Input Voltage Range <sup>1</sup> (Buffers On) | V <sub>CM</sub> Range<br>(Input Buffers On) | V <sub>CM</sub> Range<br>(Input Buffers Off) |

|-----------|------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------|----------------------------------------------|

| 1         | AGND to AVDD                                               | AGND + 100 mV to AVDD - 100 mV                         | AGND + 100 mV to AVDD – 100 mV              | AGND to AVDD <sup>2</sup>                    |

| 2         | 0 V to 500 mV                                              | 0 V to 500 mV                                          | AGND + 100 mV to AVDD – 100 mV              | AGND to AVDD <sup>2</sup>                    |

| 4         | 0 V to 250 mV                                              | 0 V to 250 mV                                          | AGND + 100 mV to AVDD – 100 mV              | AGND to AVDD <sup>2</sup>                    |

| 8         | 0 V to 125 mV                                              | 0 V to 125 mV                                          | AGND + 100 mV to AVDD – 100 mV              | AGND to AVDD <sup>2</sup>                    |

| 16        | 0 V to 62.5 mV                                             | 0 V to 62.5 mV                                         | AGND + 100 mV to AVDD - 100 mV              | AGND to AVDD <sup>2</sup>                    |

| 16 + MOD2 | 0 V to 62.5 mV                                             | 0 V to 62.5 mV                                         | AGND + 100 mV to AVDD - 100 mV              | AGND to AVDD <sup>2</sup>                    |

| 32        | 0 V to 22.18 mV                                            | 22.18 mV                                               | AGND + 100 mV to AVDD – 100 mV              | AGND to AVDD <sup>2</sup>                    |

| 32 + MOD2 | 0 V to 15.625 mV                                           | 0 V to 15.625 mV                                       | AGND + 100 mV to AVDD – 100 mV              | AGND to AVDD <sup>2</sup>                    |

| 64        | 0 V to 15.625 mV                                           | 0 V to 10.3125 mV                                      | AGND + 100 mV to AVDD – 100 mV              | AGND to AVDD <sup>2</sup>                    |

| 64 + MOD2 | 0 V to 7.8125 mV                                           | 0 V to 7.8125 mV                                       | AGND + 100 mV to AVDD – 100 mV              | AGND to AVDD <sup>2</sup>                    |

| 128       | 0 V to 7.8125 mV                                           | 0 V to 3.98 mV                                         | AGND + 100 mV to AVDD – 100 mV              | AGND to AVDD <sup>2</sup>                    |

<sup>&</sup>lt;sup>1</sup> Absolute input voltage is the differential voltage range (AIN+ to AIN-).

#### **Bipolar/Unipolar Configuration**

The analog inputs to the ADuCM362/ADuCM363 can accept either unipolar or bipolar input voltage ranges.

A bipolar voltage does not imply that the device can handle negative voltages with respect to ground. It simply means that the input range can vary above or below the common-mode voltage by the value of  $V_{\text{REF}}$  as long as the absolute input voltage range is not exceeded.

In unipolar mode, the analog input voltage range is reduced to the sum of the common-mode voltage and the positive input level; therefore, the positive input cannot go below the common-mode voltage.

<sup>&</sup>lt;sup>2</sup> If the ADC input buffers are bypassed, the common-mode voltage (V<sub>CM</sub>) is configurable rail-to-rail. However, within 200 mV of the supply rails, the input current increases.

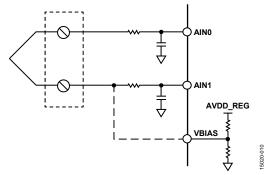

#### Fully Differential and Single-Ended Inputs

Both ADCs support two voltage input types. In fully differential mode, the user can select from any input pair to both ADCs. The external circuit determines the common-mode voltage; therefore, the external circuit must be configured to ensure that the differential signal does not exceed the minimum/maximum absolute input voltage for that input. Alternatively, the user can configure either AIN7 or AIN11 as a common-mode output pin (V<sub>BIAS</sub> mode) and then use the pin to bias the differential pair.

In single-ended mode, the negative input is selected by the ADCxCON[4:0] control bits. If the negative input pin is connected to ground and the PGA gain setting is 1, the input buffer must be bypassed. Otherwise, the negative input must be biased above the minimum input voltage value.

The PGA on both ADCs can drive the ADC modulator directly, regardless of the gain setting. Therefore, negative inputs can be connected directly to AGND.

#### **Typical ADC Modes of Operation**

The ADC can be configured to operate in one of three general modes of operation: conversion mode, calibration mode, or power-down mode.

#### **ADC Conversion Mode**

The ADC conversion mode can be used to initiate continuous conversions at a fixed rate or single conversions triggered by software.

- Single conversion: A single ADC conversion can be initiated in software by setting Bit 1 of the ADC0MDE/ADC1MDE registers. (ADCxMDE[2:0] = 010). After a single conversion is completed, the ADC returns to idle mode.

- Continuous conversion: Continuous conversion can be initiated in software by setting Bit 0 of the ADC0MDE/ADC1MDE registers. (ADCxMDE[2:0] = 001). Continuous conversion mode results in the ADCxDAT register being updated at the sampling rate selected by the ADCxFLT register.

When a conversion completes in either mode, the ADCxRDY bit (ADCxSTA[0]) is asserted, indicating that the ADC result is present in the ADC0DAT, ADC1DAT, or STEPDAT register and is available for reading. ADCxRDY and the output of the sinc2 filter can be configured to flag an interrupt to the ARM Cortex-M3 processor. If an error occurs in the conversion due to an underrange or overrange error in the input voltage of either ADC, the error is set in the appropriate ADCxSTA[4] register.

Also check the ADC comparator threshold bit (ADCxSTA[2]) as part of the ADC interrupt handler to ensure that the 1 V PGA output limit is not exceeded (see the PGA Gain Configuration section for more information).

#### **ADC Calibration Mode**

The ADC calibration mode removes ADC and system error where possible.

ADCxOF and ADCxGN registers can be written to only when the ADC is in idle mode.

It is recommended that a system zero-scale and system full-scale calibration be performed using the required system PGA gain setting. Before entering any calibration mode, the ADC being calibrated must first be in idle mode (ADCxMDE[2:0] = 011). In addition, the

- Internal zero-scale calibration.

- In this mode, an offset calibration is performed on any enabled ADC using an internally generated 0 V signal. The calibration is carried out at the user-programmed ADC settings; therefore, as with a normal single ADC conversion, it takes two to three ADC conversion cycles before a fully settled calibration result is ready. The calibration result is automatically written to the ADCxOF register of the respective ADC and ADCxSTA[5] is set to 1 to indicate the completion of the calibration command. After a reset of the device, the ADCxOF register is reloaded with the factory calibration value.

- Internal full-scale calibration (available only when gain = 1).

In this mode, a gain calibration against an internal full-scale reference voltage is performed on all enabled ADCs. A gain calibration is a two-stage process and takes twice the time of an offset calibration. The calibration result is automatically written to the ADC gain register of the respective ADC, and ADCxSTA[5] is set to 1 to indicate the completion of the calibration command. The internal full-scale calibration works for gain = 1 only. After a reset of the device, the ADC gain register is reloaded with the factory calibration value.

- System zero-scale calibration.

In this mode, a zero scale calibration is

- In this mode, a zero-scale calibration is performed on enabled ADC channels against an external zero-scale voltage driven at the ADC input pins. Usually, the selected channel is shorted externally. The calibration result is automatically written to the ADCxOF MMR of the respective ADC, and ADCxSTA[5] is set to 1 to indicate the completion of the calibration command. After a reset of the device, the ADCxOF register is reloaded with the factory calibration value.

- System full-scale calibration.

- In this mode, a full-scale calibration is performed using the enabled ADC channels against an external full-scale voltage driven at the ADC input pins. The ADC gain register is updated after a full-scale calibration sequence, and ADCxSTA[5] is set to 1 to indicate the completion of the calibration command. After a reset of the device, the ADC gain register is reloaded with the factory calibration value.

Note that the ADC gain and ADCOF registers can be modified by the user only when the ADC is in idle mode (ADCxMDE[2:0] = 011). The following separate ADC gain registers are provided for the ADCs when the reference source is the internal reference, external reference, or AVDD supply: ADCxINTGN, ADCxEXTGN, and ADCxVDDGN. Only the ADCxINTGN is loaded with a factory calibration value. The ADCxEXTGN and ADCxVDDGN registers must be updated by the user after a reset sequence.

#### ADC Power-Down Mode

Power down the ADC to reduce overall system power consumption, particularly between single conversions.

In full power-down mode, the ADCs and the input amplifiers are fully powered off for maximum power reduction. In idle mode, the ADC is fully powered on but is held in reset. The device enters this mode after calibration or between single conversions. The current consumption is reduced relative to fully active mode.

#### **OTHER ADC SUPPORT CIRCUITS**

#### **Voltage Reference Sources**

Four reference sources are supported by the ADuCM362/ADuCM363: internal reference, External Reference 1, External Reference 2, and AVDD.

#### Internal Reference

The internal reference is a precision 1.2 V band gap, low noise, low drift reference. See the ADuCM362/ADuCM363 data sheet for more information.

#### **External Reference 1**

External Reference 1 is connected to the VREF+ and VREF- pins. An option to internally buffer the external reference is also provided. A separate buffer is provided for the positive and negative external reference inputs. If the negative input is ground, bypass the negative input buffer.

#### **External Reference 2**

External Reference 2 can be connected to the AIN7/VBIAS0/IEXC/EXTREF2IN+ and AIN8/EXTREF2IN- pins. External Reference 2 offers the option of buffering the positive input to EXTREF2IN+ (see the description of ADCxCFG[2:0] in Table 30 for more details).

#### AVDD

The AVDD of the device can be selected as a reference source.

#### **Reference Detection Circuit**

An internal circuit for detecting an error on the external reference pins is available. The detection circuit checks for open-circuit conditions on the VREF+ and VREF- pins. It also checks that the differential voltage between VREF+ and VREF- is greater than 400 mV. If an error condition is detected, the error flag in the DETSTA[3] register is set.

If an external reference is selected, the on-chip reference voltage detection circuit flags an error if an open is detected on the VREF+ or VREF- pin or if the differential input reference voltage across VREF+/VREF- is below 400 mV. In normal operation, the sampling rate is configured via the ADCxFLT registers.

No reference detection circuit is available for the EXTREF2IN± pins.

#### Fast Response Output/Input Step Detection Circuit

On both ADCs, the output of the  $\Sigma$ - $\Delta$  modulator is fed into a sinc3 or sinc4 digital filter. However, for faster response times, a sinc2 filter can be selected to operate in parallel with the sinc3 or sinc4 filter of both ADCs, but the sinc3 and sinc4 filters cannot operate simultaneously. This sinc2 filter has a configurable update rate with a fastest speed of 2 ms and with 14 effective bits resolution. The output of the sinc2 filter is fed to a separate result register, STEPDAT.

The sinc2 filter can also be used in step detection mode for detecting step changes in the input signal. In this mode, the output of the sinc2 filter is compared with the two previous output values. If the difference between the latest value and the two previous values is greater than a predefined step threshold, a step detected flag is asserted in the DETSTA register and an interrupt is triggered. Alternatively, a step can be triggered by comparing the output of the sinc2 filter with the last output of the sinc3 or sinc4 filter. If the difference is greater than the configured threshold level, the step detected flag is asserted.

Two possible interrupt sources are provided with the sinc2 filter:

- Using the DMA controller and the associated ADC DMA interrupt; when a preconfigured number of sinc2 samples is stored to memory, this interrupt flag is set.

- A separate interrupt flag is provided for the step detection filter (DETSTA[1]).

The DETCON register configures the sinc2 filter and step detection circuit.

Every output from the sinc2 filter can be read by polling DETSTA[0].

#### **Step Detection Circuit**

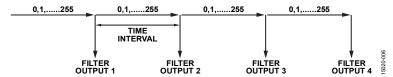

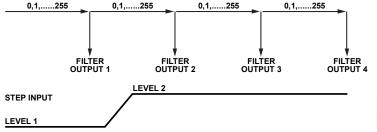

As Figure 7 shows, the step detection filter uses  $256 \times ADC$  clocks for each sample period. The output at the end of each filter period is the average value of each of the 256 samples. The step detection hardware compares each output with the three previous outputs. If the difference between the current output and any of the previous outputs is greater than the selected threshold level, a step is detected. The oversampling rate of the sinc2 filter is configurable for  $256/512/768/1024 \times ADC$  clocks, resulting in sampling periods of 2 ms/4 ms/6 ms/8 ms, respectively, by setting DETCON[1:0].

Figure 7. ADuCM362/ADuCM363 Step Detection Timing Diagram

As Figure 8 shows, the difference between Level 1 and Level 2 is greater than the selected threshold level:

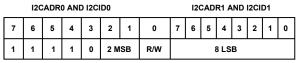

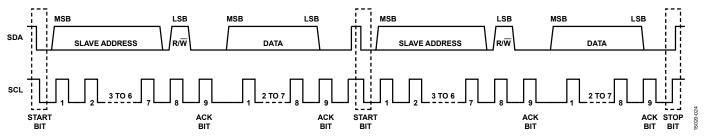

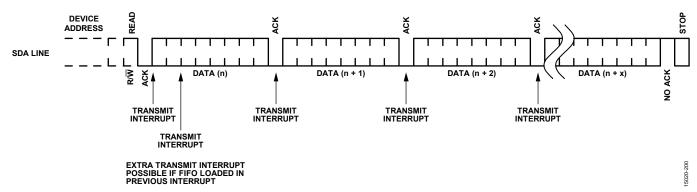

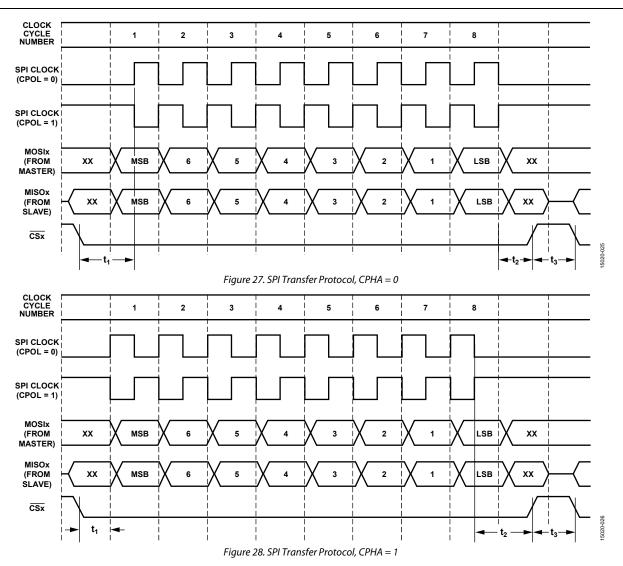

- If Output 4 Output 3 = result < threshold, then no step detected.