#### **Features**

- Incorporates the ARM7TDMI<sup>®</sup> ARM<sup>®</sup> Thumb<sup>®</sup> Processor Core

- High-performance 32-bit RISC Architecture

- High-density 16-bit Instruction Set

- Leader in MIPS/Watt

- Little-endian

- EmbeddedICE<sup>™</sup> (In-circuit Emulation)

- 8-, 16- and 32-bit Read and Write Support

- 256K Bytes of On-chip SRAM

- 32-bit Data Bus

- Single-clock Cycle Access

- Fully-programmable External Bus Interface (EBI)

- Maximum External Address Space of 64M Bytes

- Up to Eight Chip Selects

- Software Programmable 8/16-bit External Data Bus

- · Eight-level Priority, Individually Maskable, Vectored Interrupt Controller

- Four External Interrupts, Including a High-priority, Low-latency Interrupt Request

- 32 Programmable I/O Lines

- Three-channel 16-bit Timer/Counter

- Three External Clock Inputs

- Two Multi-purpose I/O Pins per Channel

- Two USARTs

- Two Dedicated Peripheral Data Controller (PDC) Channels per USART

- Programmable Watchdog Timer

- Advanced Power-saving Features

- CPU and Peripheral Can be Deactivated Individually

- Fully Static Operation

- 0 Hz to 75 MHz Internal Frequency Range at V<sub>DDCORE</sub> = 1.8V, 85°C

- 2.7V to 3.6V I/O Operating Range

- 1.65V to 1.95V Core Operating Range

- Available in 100-lead TQFP Package

- -40° C to +85° C Temperature Range

# 1. Description

The AT91R40008 microcontroller is a member of the Atmel AT91 16-/32-bit microcontroller family, which is based on the ARM7TDMI processor core. This processor has a high-performance, 32-bit RISC architecture with a high-density, 16-bit instruction set and very low power consumption. Furthermore, it features 256K bytes of on-chip SRAM and a large number of internally banked registers, resulting in very fast exception handling, and making the device ideal for real-time control applications.

The AT91R40008 microcontroller features a direct connection to off-chip memory, including Flash, through the fully-programmable External Bus Interface (EBI). An 8-level priority vectored interrupt controller, in conjunction with the Peripheral Data Controller, significantly improves the real-time performance of the device.

The device is manufactured using Atmel's high-density CMOS technology. By combining the ARM7TDMI processor core with a large, on-chip, high-speed SRAM and a wide range of peripheral functions on a monolithic chip, the AT91R40008 is a powerful microcontroller that offers a flexible and high-performance solution to many compute-intensive embedded control applications.

# AT91 ARM® Thumb® Microcontrollers

# AT91R40008 Electrical Characteristics

# 2. Absolute Maximum Ratings\*

Operating Temperature (Industrial) .. -40° C to + 85° C

Storage Temperature ...... -60° C to + 150° C

Voltage on Any Input Pin with Respect to Ground

...... -0.3V to max of V<sub>DDIO</sub>

...... + 0.3V and 3.6V

Maximum Operating Voltage (V<sub>DDIO</sub>) .......3.6V

Maximum Operating Voltage (V<sub>DDCORE</sub>) .......1.95V

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **DC Characteristics** 3.

The following characteristics are applicable to the Operating Temperature range:  $T_A = -40^{\circ}$  C to +85° C, unless otherwise specified and are certified for a Junction Temperature up to 100° C.

**Table 3-1.** DC Characteristics

| Symbol              | Parameter             | Conditions                                                          |                        | Min                     | Тур | Max                         | Units |

|---------------------|-----------------------|---------------------------------------------------------------------|------------------------|-------------------------|-----|-----------------------------|-------|

| V <sub>DDIO</sub>   | DC Supply I/Os        |                                                                     |                        | 2.7                     |     | 3.6                         | ٧     |

| V <sub>DDCORE</sub> | DC Supply Core        |                                                                     |                        | 1.65                    |     | 1.95                        | ٧     |

| V <sub>IL</sub>     | Input Low Voltage     |                                                                     |                        | -0.3                    |     | 0.8                         | ٧     |

| V <sub>IH</sub>     | Input High Voltage    |                                                                     |                        | 2.0                     |     | V <sub>DDIO</sub> + 0<br>.3 | V     |

|                     |                       | Pin Group 1 <sup>(2)</sup> : I <sub>OL</sub> = 16 mA <sup>(1)</sup> |                        |                         |     | 0.4                         | V     |

|                     | Outrout Law Valle as  | Pin Group 2 <sup>(3)</sup> : I <sub>OL</sub> = 8 mA <sup>(1)</sup>  |                        |                         |     | 0.4                         | ٧     |

| V <sub>OL</sub>     | Output Low Voltage    | Pin Group 3 <sup>(4)</sup> : I <sub>OL</sub> = 2 mA <sup>(1)</sup>  |                        |                         |     | 0.4                         | V     |

|                     |                       | All Output Pins: I <sub>OL</sub> = 0 mA <sup>(1)</sup>              |                        |                         |     | 0.2                         | V     |

|                     |                       | Pin Group 1 <sup>(2)</sup> : I <sub>OH</sub> = 16 mA <sup>(1)</sup> |                        | V <sub>DDIO</sub> - 0.4 |     |                             | ٧     |

| V <sub>OH</sub>     |                       | Pin Group 2 <sup>(3)</sup> : I <sub>OH</sub> = 8 mA <sup>(1)</sup>  |                        | V <sub>DDIO</sub> - 0.4 |     |                             |       |

| V <sub>OH</sub>     | Output High Voltage   | Pin Group 3 <sup>(4)</sup> : I <sub>OH</sub> = 2 mA <sup>(1)</sup>  |                        | V <sub>DDIO</sub> - 0.4 |     |                             |       |

|                     |                       | All Output Pins: I <sub>OH</sub> = 0 mA <sup>(1)</sup>              |                        | V <sub>DDIO</sub> - 0.2 |     |                             |       |

| I <sub>LEAK</sub>   | Input Leakage Current |                                                                     |                        |                         |     | 10                          | μA    |

| I <sub>PULL</sub>   | Input Pull-up Current | $V_{DDIO} = 3.6V, V_{IN} = 0V$                                      |                        |                         |     | 280                         | μA    |

|                     |                       | Pin Group 1 <sup>(2)</sup>                                          |                        |                         |     | 16                          | mA    |

| I <sub>OUT</sub>    | Output Current        | Pin Group 2 <sup>(3)</sup> :                                        |                        |                         |     | 8                           | mA    |

|                     |                       | Pin Group 3 <sup>(4)</sup> :                                        |                        |                         |     | 2                           | mA    |

| C <sub>IN</sub>     | Input Capacitance     | TQFP100 Package                                                     |                        |                         |     | 5.3                         | pF    |

|                     | Obalia Ossessal       | VDDIO= 3.6V, V <sub>DDCORE</sub> = 1.95V,<br>MCKI = 0Hz             | T <sub>A</sub> = 25° C |                         |     | 120                         | μΑ    |

| I <sub>SC</sub>     | Static Current        | All Inputs Driven<br>TMS, TCK, TDI, NRST = 1                        | T <sub>A</sub> = 85° C |                         |     | 2.3                         | mA    |

- Notes: 1.  $I_{OL}$  = Output Current at low level.  $I_{OH}$ = Output Current at high level.

- 2. Pin Group 1 = NUB/NWR1, NWE/NWR0, NOE/NRD1

- 3. Pin Group 2 = D0-D15, A0/NLB, A1-A19, P28/A20/CS7, P29/A21/CS6, P30/A22/CS5, P31/A23/CS4, NCS0, NCS1, P26/NCS2, P27/NCS3

- 4. Pin Group 3 = All Others

# 4. Power Consumption

The values in the following tables are values measured in the typical operating conditions (i.e.,  $V_{DDIO} = 3.3V$ ,  $V_{DDCORE} = 1.8V$ ,  $T_A = 25^{\circ}C$ ) on the AT91EB40A Evaluation Board and are given as demonstrative values.

**Table 4-1.** Power Consumption

| Mode   | Conditions                                                                              | Consumption | Unit   |

|--------|-----------------------------------------------------------------------------------------|-------------|--------|

| Reset  |                                                                                         | 0.02        |        |

|        | Fetch in ARM mode from internal SRAM<br>All peripheral clocks activated                 | 0.83        |        |

| Navasi | Fetch in ARM mode from internal SRAM All peripheral clocks deactivated                  | 0.73        |        |

| Normal | Fetch in ARM mode from external SRAM <sup>(1)</sup> All peripheral clocks deactivated   | 0.20        | mW/MHz |

|        | Fetch in Thumb mode from external SRAM <sup>(1)</sup> All peripheral clocks deactivated | 0.24        |        |

| Idlo   | All peripheral clocks activated                                                         | 0.16        | 1      |

| Idle   | All peripheral clocks deactivated                                                       | 0.06        |        |

Note: 1. With two Wait States.

**Table 4-2.** Power Consumption per Peripheral

| Peripheral                       | Consumption | Unit       |

|----------------------------------|-------------|------------|

| PIO Controller                   | 15.3        |            |

| Timer/Counter Channel            | 15.0        | \\//\\.4Ы→ |

| Timer/Counter Block (3 Channels) | 36.3        | μW/MHz     |

| USART                            | 27.8        |            |

# 4.1 Thermal and Reliability Considerations

#### 4.1.1 Thermal Data

In Table 4-3, the device lifetime is estimated with the MIL-217 standard in the "moderately controlled" environmental model (this model is described as corresponding to an installation in a permanent rack with adequate cooling air), depending on the device Junction Temperature. (For details see the section "Junction Temperature" on page 5.)

Note that the user must be extremely cautious with this MTBF calculation: as the MIL-217 model is pessimistic with respect to observed values due to the way the data/models are obtained (test under severe conditions). The life test results that have been measured are always better than the predicted ones.

**Table 4-3.** MTBF Versus Junction Temperature

| Junction Temperature (T <sub>J</sub> ) (°C) | Estimated Lifetime (MTBF) (Year) |

|---------------------------------------------|----------------------------------|

| 100                                         | 10                               |

| 125                                         | 5                                |

| 150                                         | 3                                |

| 175                                         | 2                                |

Table 4-4 summarizes the thermal resistance data related to the package of interest.

Table 4-4. Thermal Resistance Data

| Symbol        | Parameter                              | Condition | Package | Тур | Unit |

|---------------|----------------------------------------|-----------|---------|-----|------|

| $\theta_{JA}$ | Junction-to-ambient thermal resistance | Still Air | TQFP100 | 40  | °C/M |

| $\theta_{JC}$ | Junction-to-case thermal resistance    |           | TQFP100 | 6.4 | °C/W |

### 4.1.2 Reliability Data

The number of gates and the device die size are provided for the user to calculate reliability data with another standard and/or in another environmental model.

Table 4-5. Reliability Data

| Parameter              | Data   | Unit            |

|------------------------|--------|-----------------|

| Number of Logic Gates  | 280    | K gates         |

| Number of Memory Gates | 12,897 | K gates         |

| Device Die Size        | 21.2   | mm <sup>2</sup> |

# 4.2 Junction Temperature

The average chip-junction temperature T<sub>J</sub> in °C can be obtained from the following:

1.

$$T_J = T_A + (P_D \times \theta_{JA})$$

2.

$$T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$$

#### Where:

- $\theta_{JA}$  = package thermal resistance, Junction-to-ambient (°C/W), provided in Table 4-4 on page 5.

- $\theta_{JC}$ = package thermal resistance, Junction-to-case thermal resistance (°C/W), provided in Table 4-4 on page 5.

- $\theta_{\textit{HEAT SINK}}$  = cooling device thermal resistance (°C/W), provided in the device datasheet.

- P<sub>D</sub> = device power consumption (W) estimated from data provided in the section "Power Consumption" on page 4.

- T<sub>A</sub> = ambient temperature (°C).

From the first equation, the user can derive the estimated lifetime of the chip and thereby decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_{ij}$  in °C

# 5. Conditions

# 5.1 Timing Results

The delays are given as typical values in the following conditions:

- $V_{DDIO} = 3.0 \text{V}$

- *V<sub>DDCORE</sub>* = 1.8V

- Ambient Temperature = 25° C

- Load Capacitance = 0 pF

- The output level change detection is 0.5 x V<sub>DDIO</sub>

- The input level is 0.8V for a low-level detection and is 2.0V for a high level detection.

The minimum and maximum values given in the AC characteristic tables of this datasheet take into account the process variation and the design.

In order to obtain the timing for other conditions, the following equation should be used:

$$t = \delta_{T^{\circ}} \times \left( (\delta_{VDDCORE} \times t_{DATASHEET}) + \left( \delta_{VDDIO} \times \sum C_{SIGNAL} \times \delta_{CSIGNAL}) \right) \right)$$

#### Where:

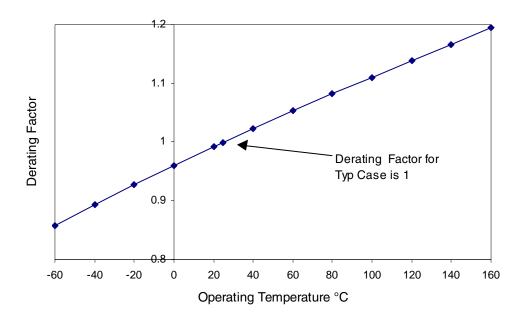

- $\delta_{\tau}^{\circ}$  is the derating factor in temperature given in Figure 5-1.

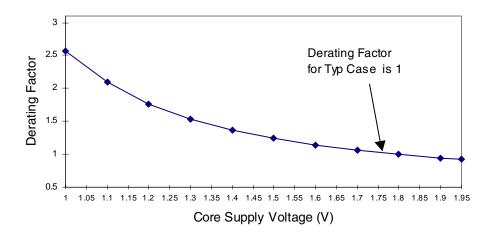

- $\delta_{VDDCORE}$  is the derating factor for the Core Power Supply given in Figure 5-2 on page 7.

- t<sub>DATASHEET</sub> is the minimum or maximum timing value given in this datasheet for a load capacitance of 0 pF.

- $\delta_{VDDIO}$  is the derating factor for the I/O Power Supply given in Figure 5-3 on page 8.

- $C_{SIGNAL}$  is the capacitance load on the considered output pin.<sup>(1)</sup>

- $\delta_{CSIGNAL}$  is the load derating factor depending on the capacitance load on the related output pins given in Min and Max values in this datasheet.

The input delays are given as typical values.

Note: The user must take into account the package capacitance load contribution ( $C_{IN}$ ) described in Table 3-1 on page 3.

# 5.2 Temperature Derating Factor

Figure 5-1. Derating Curve for Different Operating Temperatures

# 5.3 Core Voltage Derating Factor

Figure 5-2. Core Voltage Derating Factor

# 5.4 IO Voltage Derating Factor

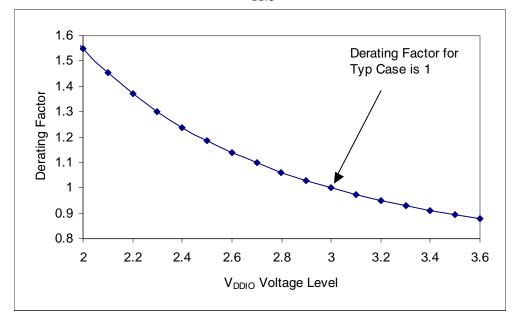

**Figure 5-3.** Derating Factor for Different V<sub>DDIO</sub> Power Supply Levels

# 6. Clock Waveforms

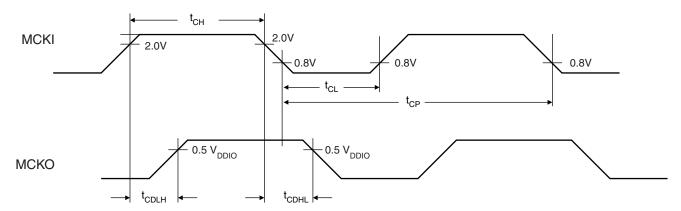

Table 6-1.

Master Clock Waveform Parameters

| Symbol               | Parameter            | Conditions | Min  | Max  | Units |

|----------------------|----------------------|------------|------|------|-------|

| 1/(t <sub>CP</sub> ) | Oscillator Frequency |            |      | 82.1 | MHz   |

| t <sub>CP</sub>      | Oscillator Period    |            | 12.2 |      | ns    |

| t <sub>CH</sub>      | High Half-period     |            | 5.0  |      | ns    |

| t <sub>CL</sub>      | Low Half-period      |            | 5.5  |      | ns    |

Table 1. Clock Propagation Times

| Symbol            | Parameter                     | Conditions                 | Min   | Max   | Units |

|-------------------|-------------------------------|----------------------------|-------|-------|-------|

| t <sub>CDLH</sub> | Rising Edge Propagation Time  | C <sub>MCKO</sub> = 0 pF   | 4.4   | 6.6   | ns    |

|                   |                               | C <sub>MCKO</sub> derating | 0.199 | 0.295 | ns/pF |

|                   | Falling Edge Dropagation Time | C <sub>MCKO</sub> = 0 pF   | 4.5   | 6.7   | ns    |

| <sup>T</sup> CDHL | Falling Edge Propagation Time | C <sub>MCKO</sub> derating | 0.153 | 0.228 | ns/pF |

Figure 6-1. Clock Waveform

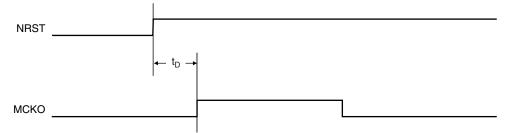

Table 6-2. NRST to MCKO

| Symbol         | Parameter                           | Min                   | Max                   | Units |

|----------------|-------------------------------------|-----------------------|-----------------------|-------|

| t <sub>D</sub> | NRST Rising Edge to MCKO Valid Time | 3(t <sub>CP</sub> /2) | 7(t <sub>CP</sub> /2) | ns    |

Figure 6-2. MCKO Relative to NRST

# 7. AC Characteristics

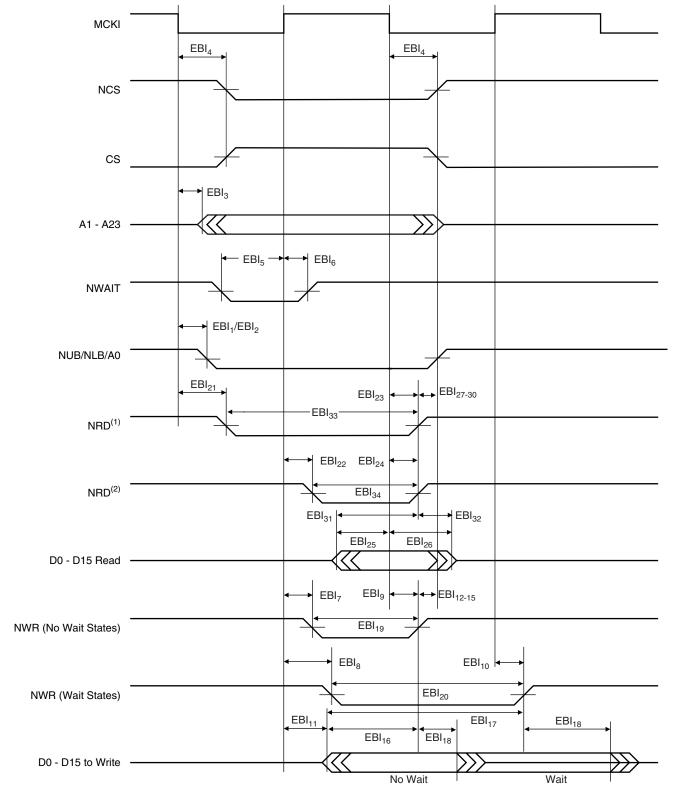

# 7.1 EBI Signals Relative to MCKI

The following tables show timings relative to operating condition limits defined in the section "Timing Results" on page 6. See Figure 7-1 on page 14.

Table 7-1. General-purpose EBI Signals

| Symbol           | Parameter                      | Conditions                | Min   | Max                                                 | Units |

|------------------|--------------------------------|---------------------------|-------|-----------------------------------------------------|-------|

| EDI              | MOKI Falkin a ta NILID Valkal  | C <sub>NUB</sub> = 0 pF   | 4.4   | 8.9                                                 | ns    |

| EBI <sub>1</sub> | MCKI Falling to NUB Valid      | C <sub>NUB</sub> derating | 0.030 | -                                                   | ns/pF |

| EDI              | MCKI Folling to NI P/A0 Volid  | C <sub>NLB</sub> = 0 pF   | 3.7   | 8.9<br>0.043<br>6.7<br>0.069<br>7.8<br>0.076<br>8.6 | ns    |

| EBI <sub>2</sub> | MCKI Falling to NLB/A0 Valid   | C <sub>NLB</sub> derating | 0.045 | 0.069                                               | ns/pF |

| EDI              | MCKI Folling to A1 A00 Volid   | C <sub>ADD</sub> = 0 pF   | 3.4   | 7.8                                                 | ns    |

| EBI <sub>3</sub> | MCKI Falling to A1 - A23 Valid | C <sub>ADD</sub> derating | 0.045 | 8.9<br>0.043<br>6.7<br>0.069<br>7.8<br>0.076<br>8.6 | ns/pF |

| EDI              | MCKI Falling to Chip Select    | C <sub>NCS</sub> = 0 pF   | 3.7   | 8.6                                                 | ns    |

| EBI <sub>4</sub> | Change                         | C <sub>NCS</sub> derating | 0.045 | 0.078                                               | ns/pF |

| EBI <sub>5</sub> | NWAIT Setup before MCKI Rising |                           | 1.7   |                                                     | ns    |

| EBI <sub>6</sub> | NWAIT Hold after MCKI Rising   |                           | 1.7   |                                                     | ns    |

Table 7-2.EBI Write Signals

| Symbol                                                      | Parameter                                      | Conditions                 | Min   | Max                                                                                                                                                                                                                                                                                                 | Units |

|-------------------------------------------------------------|------------------------------------------------|----------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| - FDI                                                       | MCKI Dising to NIMD Active (No Meit States)    | C <sub>NWR</sub> = 0 pF    | 3.9   | 6.3                                                                                                                                                                                                                                                                                                 | ns    |

| EBI <sub>7</sub>                                            | MCKI Rising to NWR Active (No Wait States)     | C <sub>NWR</sub> derating  | 0.029 |                                                                                                                                                                                                                                                                                                     | ns/pF |

| - FDI                                                       | MCKI Diging to NIMD Active (IMeit States)      | C <sub>NWR</sub> = 0 pF    | 4.4   | 7.0                                                                                                                                                                                                                                                                                                 | ns    |

| EBI <sub>8</sub>                                            | MCKI Rising to NWR Active (Wait States)        | C <sub>NWR</sub> derating  | 0.029 | 0.043                                                                                                                                                                                                                                                                                               | ns/pF |

| EDI                                                         | MCKI Folling to NIMP Inpeting (No Weit States) | C <sub>NWR</sub> = 0 pF    | 3.8   | 6.3                                                                                                                                                                                                                                                                                                 | ns    |

| EDI <sub>9</sub>                                            | MCKI Falling to NWR Inactive (No Wait States)  | C <sub>NWR</sub> derating  | 0.029 | 0.044                                                                                                                                                                                                                                                                                               | ns/pF |

| - FDI                                                       | MCKI Dising to NIMD Inactive (Mait States)     | C <sub>NWR</sub> = 0 pF    | 4.2   | 6.7                                                                                                                                                                                                                                                                                                 | ns    |

| EDI <sub>10</sub>                                           | MCKI Rising to NWR Inactive (Wait States)      | C <sub>NWR</sub> derating  | 0.029 | 4.4     7.0       0.029     0.043       3.8     6.3       0.029     0.044       4.2     6.7       0.029     0.044       4.2     7.5       0.045     0.080       3.1     7.0       0.030     0.043       3.1     5.4       0.043     0.073                                                           | ns/pF |

| - FDI                                                       | MCKI Diging to DO D15 Out Volid                | C <sub>DATA</sub> = 0 pF   | 4.2   | 7.5                                                                                                                                                                                                                                                                                                 | ns    |

| EDI <sub>11</sub>                                           | MCKI Rising to D0 - D15 Out Valid              | C <sub>DATA</sub> derating | 0.045 | 0.080                                                                                                                                                                                                                                                                                               | ns/pF |

| - FDI                                                       | NIMD Lighte NIID Change                        | C <sub>NUB</sub> = 0 pF    | 3.1   | 7.0                                                                                                                                                                                                                                                                                                 | ns    |

| □□1 <sub>12</sub>                                           | NWR High to NUB Change                         | C <sub>NUB</sub> derating  | 0.030 | 3.9     6.3       0.029     0.043       4.4     7.0       0.029     0.043       3.8     6.3       0.029     0.044       4.2     6.7       0.029     0.044       4.2     7.5       0.045     0.080       3.1     7.0       0.030     0.043       3.1     5.4       0.043     0.073       2.9     7.0 | ns/pF |

| - FDI                                                       | NIMP High to NI P/AO Change                    | C <sub>NLB</sub> = 0 pF    | 3.1   | 5.4                                                                                                                                                                                                                                                                                                 | ns    |

| EBI <sub>10</sub> N EBI <sub>11</sub> N EBI <sub>12</sub> N | NWR High to NLB/A0 Change                      | C <sub>NLB</sub> derating  | 0.043 | 0.073                                                                                                                                                                                                                                                                                               | ns/pF |

| EDI                                                         | NIMP High to A1 A22 Change                     | C <sub>ADD</sub> = 0 pF    | 2.9   | 7.0                                                                                                                                                                                                                                                                                                 | ns    |

| EDI <sub>14</sub>                                           | NWR High to A1 - A23 Change                    | C <sub>ADD</sub> derating  | 0.043 | 6.3<br>0.043<br>7.0<br>0.043<br>6.3<br>0.044<br>6.7<br>0.044<br>7.5<br>0.080<br>7.0<br>0.043<br>5.4<br>0.073<br>7.0                                                                                                                                                                                 | ns/pF |

Table 7-2. EBI Write Signals (Continued)

| Symbol            | Parameter                                                      | Conditions                 | Min                                      | Max   | Units |

|-------------------|----------------------------------------------------------------|----------------------------|------------------------------------------|-------|-------|

| EDI               | NIM/D Lligh to Chip Colort Inactive                            | C <sub>NCS</sub> = 0 pF    | 2.9                                      | 6.8   | ns    |

| EBI <sub>15</sub> | NWR High to Chip Select Inactive                               | C <sub>NCS</sub> derating  | 0.052                                    | 0.067 | ns/pF |

|                   |                                                                | C = 0 pF                   | t <sub>CH</sub> - 1.8                    |       | ns    |

| EBI <sub>16</sub> | Data Out Valid before NWR High (No Wait States) <sup>(1)</sup> | C <sub>DATA</sub> derating | -0.080                                   |       | ns/pF |

|                   |                                                                | C <sub>NWR</sub> derating  | 0.044                                    |       | ns/pF |

|                   |                                                                | C = 0 pF                   | n x t <sub>CP</sub> - 1.3 <sup>(2)</sup> |       | ns    |

| EBI <sub>17</sub> | Data Out Valid before NWR High (Wait States) <sup>(1)</sup>    | C <sub>DATA</sub> derating | -0.080                                   |       | ns/pF |

|                   |                                                                | C <sub>NWR</sub> derating  | 0.044                                    |       | ns/pF |

| EBI <sub>18</sub> | Data Out Valid after NWR High                                  |                            | 2.2                                      |       | ns    |

| EDI               | NIA/D Minimum Dulo Windah (No Wold Chatan)(1)                  | C <sub>NWR</sub> = 0 pF    | t <sub>CH</sub> - 0.6                    |       | ns    |

| EBI <sub>19</sub> | NWR Minimum Pulse Width (No Wait States) <sup>(1)</sup>        | C <sub>NWR</sub> derating  | 0                                        |       | ns/pF |

| EDI               | NIA/D Minimum Dulos Minimum (Mais Canas a)(1)                  | C <sub>NWR</sub> = 0 pF    | n x t <sub>CP</sub> - 0.9 <sup>(2)</sup> |       | ns    |

| EBI <sub>20</sub> | NWR Minimum Pulse Width (Wait States) <sup>(1)</sup>           | C <sub>NWR</sub> derating  | 0                                        |       | ns/pF |

Notes: 1. The derating factor should not be applied to  $t_{CH}$  or  $t_{CP}$

2. n = number of standard wait states inserted.

Table 7-3.EBI Read Signals

| Symbol            | Parameter                                                 | Conditions                | Min   | Max   | Units |

|-------------------|-----------------------------------------------------------|---------------------------|-------|-------|-------|

| EDI               | MCKI Falling to NRD Active <sup>(1)</sup>                 | C <sub>NRD</sub> = 0 pF   | 4.5   | 7.9   | ns    |

| EBI <sub>21</sub> | MCKI Falling to NRD Active                                | C <sub>NRD</sub> derating | 0.029 | 0.043 | ns/pF |

| EBI <sub>22</sub> | MCKI Rising to NRD Active <sup>(2)</sup>                  | C <sub>NRD</sub> = 0 pF   | 3.8   | 7.3   | ns    |

|                   |                                                           | C <sub>NRD</sub> derating | 0.029 | 0.043 | ns/pF |

| EDI               | MCKI Folling to NDD Inactive(1)                           | C <sub>NRD</sub> = 0 pF   | 4.1   | 6.5   | ns    |

| EBI <sub>23</sub> | MCKI Falling to NRD Inactive <sup>(1)</sup>               | C <sub>NRD</sub> derating | 0.030 | 0.044 | ns/pF |

| EDI               | MCKI Falling to NRD Inactive (2)                          | C <sub>NRD</sub> = 0 pF   | 3.9   | 5.8   | ns    |

| EBI <sub>24</sub> |                                                           | C <sub>NRD</sub> derating | 0.030 | 0.044 | ns/pF |

| EBI <sub>25</sub> | D0 - D15 In Setup before MCKI Falling Edge <sup>(5)</sup> |                           | 1.5   |       | ns    |

| EBI <sub>26</sub> | D0 - D15 In Hold after MCKI Falling Edge <sup>(6)</sup>   |                           | 1.2   |       | ns    |

| EDI               | NDD High to NHD Charge                                    | C <sub>NUB</sub> = 0 pF   | 3.2   | 7.1   | ns    |

| EBI <sub>27</sub> | NRD High to NUB Change                                    | C <sub>NUB</sub> derating | 0.030 | 0.043 | ns/pF |

| EDI               | NRD High to NLB/A0 Change                                 | C <sub>NLB</sub> = 0 pF   | 3.2   | 4.6   | ns    |

| EBI <sub>28</sub> |                                                           | C <sub>NLB</sub> derating | 0.043 | 0.073 | ns/pF |

| EDI               | NIDD III I AA ACC CI                                      | C <sub>ADD</sub> = 0 pF   | 2.8   | 6.1   | ns    |

| EBI <sub>29</sub> | NRD High to A1 - A23 Change                               | C <sub>ADD</sub> derating | 0.043 | 0.076 | ns/pF |

| EDI               | NDD High to Chin Coloct Inceting                          | C <sub>NCS</sub> = 0 pF   | 2.9   | 6.2   | ns    |

| EBI <sub>30</sub> | NRD High to Chip Select Inactive                          | C <sub>NCS</sub> derating | 0.052 | 0.067 | ns/pF |

**Table 7-3. EBI Read Signals**

| Symbol            | Parameter                                  | Conditions                | Min                                                          | Max | Units |

|-------------------|--------------------------------------------|---------------------------|--------------------------------------------------------------|-----|-------|

| EDI               | Data Catura hadaya NDD High (6)            | C <sub>NRD</sub> = 0 pF   | 8.0                                                          |     | ns    |

| EBI <sub>31</sub> | Data Setup before NRD High <sup>(6)</sup>  | C <sub>NRD</sub> derating | 0.044                                                        |     | ns/pF |

| EDI               | Data Hald offer NDD High (6)               | C <sub>NRD</sub> = 0 pF   | -3.1                                                         |     | ns    |

| EBI <sub>32</sub> | Data Hold after NRD High <sup>(6)</sup>    | C <sub>NRD</sub> derating | -0.030                                                       |     | ns/pF |

| EBI <sub>33</sub> | NRD Minimum Pulse Width <sup>(1) (3)</sup> | C <sub>NRD</sub> = 0 pF   | (n +1) t <sub>CP</sub> - 1.9 <sup>(4)</sup>                  |     | ns    |

|                   |                                            | C <sub>NRD</sub> derating | 0.001                                                        |     | ns/pF |

| EBI <sub>34</sub> |                                            | C <sub>NRD</sub> = 0 pF   | n x t <sub>CP</sub> + (t <sub>CH</sub> - 1.5) <sup>(4)</sup> |     | ns    |

|                   | NRD Minimum Pulse Width <sup>(2) (3)</sup> | C <sub>NRD</sub> derating | 0.001                                                        |     | ns/pF |

Notes: 1. Early Read Protocol.

- 2. Standard Read Protocol.

- 3. The derating factor should not be applied to  $t_{CH}$  or  $t_{CP}$

- 4. n = number of standard wait states inserted.

- 5. Only one of these two timings,  $EB_{25}$  or  $EBI_{31}$ , needs to be met.

- 6. Only one of these two timings,  $EB_{26}$  or  $EBI_{32}$ , needs to be met.

**Table 7-4.** EBI Read and Write Control Signals. Capacitance Limitation

| Symbol                             | Parameter                               | Conditions                | Min   | Max | Units |

|------------------------------------|-----------------------------------------|---------------------------|-------|-----|-------|

| T <sub>CPLNRD</sub> <sup>(1)</sup> | Master Clock Low Due to NRD Capacitance | C <sub>NRD</sub> = 0 pF   | 7.3   |     | ns    |

|                                    |                                         | C <sub>NRD</sub> derating | 0.044 |     | ns/pF |

| <b>T</b> (2)                       | Master CLock Low Due to NWR Capacitance | C <sub>NWR</sub> = 0 pF   | 7.6   |     | ns    |

| I CPLNWR (2)                       |                                         | C <sub>NWR</sub> derating | 0.044 |     | ns/pF |

- Notes: 1. If this condition is not met, the action depends on the read protocol intended for use.

- Early Read Protocol: Programing an additional t<sub>DF</sub> (Data Float Output Time) cycle.

- Standard Read Protocol: Programming an additional t<sub>DF</sub> Cycle and an additional wait state.

- 2. Applicable only for chip select programmed with 0 wait state. If this condition is not met, at least one wait state must be programmed.

Figure 7-1. EBI Signals Relative to MCKI

Notes: 1. Early Read Protocol.

14

2. Standard Read Protocol.

# 7.2 Peripheral Signals

#### 7.2.1 USART Signals

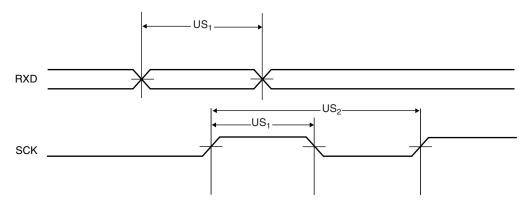

The inputs have to meet the minimum pulse width and period constraints shown in Table 7-5 and Table 7-6, and represented in Figure 7-2.

Table 7-5. USART Input Minimum Pulse Width

| Symbol          | Parameter                   | Min Pulse Width       | Units |

|-----------------|-----------------------------|-----------------------|-------|

| US <sub>1</sub> | SCK/RXD Minimum Pulse Width | 5(t <sub>CP</sub> /2) | ns    |

Table 7-6. USART Minimum Input Period

| Symbol          | Parameter                | Min Input Period      | Units |

|-----------------|--------------------------|-----------------------|-------|

| US <sub>2</sub> | SCK Minimum Input Period | 9(t <sub>CP</sub> /2) | ns    |

Figure 7-2. USART Signals

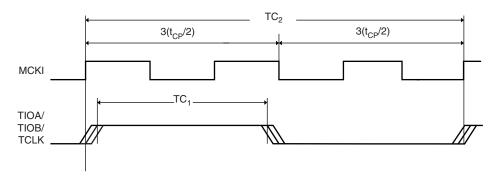

#### 7.2.2 Timer/Counter Signals

Due to internal synchronization of input signals, there is a delay between an input event and a corresponding output event. This delay is  $3(t_{CP})$  in Waveform Event Detection mode and  $4(t_{CP})$  in Waveform Total-count Detection mode. The inputs have to meet the minimum pulse width and minimum input period shown in Table 7-7 and Table 7-8, and as represented in Figure 7-3.

Table 7-7. Timer Input Minimum Pulse Width

| Symbol          | Parameter                          | Min Pulse Width       | Units |

|-----------------|------------------------------------|-----------------------|-------|

| TC <sub>1</sub> | TCLK/TIOA/TIOB Minimum Pulse Width | 3(t <sub>CP</sub> /2) | ns    |

**Table 7-8.** Timer Input Minimum Period

| Symbol          | Parameter                           | Min Input Period      | Units |

|-----------------|-------------------------------------|-----------------------|-------|

| TC <sub>2</sub> | TCLK/TIOA/TIOB Minimum Input Period | 5(t <sub>CP</sub> /2) | ns    |

Figure 7-3. Timer Input

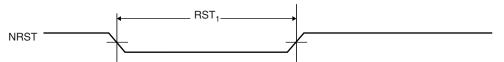

### 7.2.3 Reset Signals

A minimum pulse width is necessary, as shown in Table 7-9 and as represented in Figure 7-4.

Table 7-9. Reset Minimum Pulse Width

| Symbol           | Parameter                | Min Pulse-width      | Units |

|------------------|--------------------------|----------------------|-------|

| RST <sub>1</sub> | NRST Minimum Pulse Width | 10(t <sub>CP</sub> ) | ns    |

Figure 7-4. Reset Signal

Only the NRST rising edge is synchronized with MCKI. The falling edge is asynchronous.

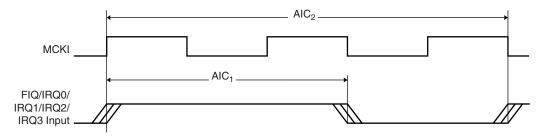

### 7.2.4 Advanced Interrupt Controller Signals

Inputs have to meet the minimum pulse width and minimum input period shown in Table 7-10 and Table 7-11 and represented in Figure 7-5.

Table 7-10. AIC Input Minimum Pulse Width

| Symbol           | Parameter                                   | Min Pulse Width       | Units |

|------------------|---------------------------------------------|-----------------------|-------|

| AIC <sub>1</sub> | FIQ/IRQ0/IRQ1/IRQ2/IRQ3 Minimum Pulse Width | 3(t <sub>CP</sub> /2) | ns    |

Table 7-11. AIC Input Minimum Period

| Symbol           | Parameter                | Min Input Period      | Units |

|------------------|--------------------------|-----------------------|-------|

| AIC <sub>2</sub> | AIC Minimum Input Period | 5(t <sub>CP</sub> /2) | ns    |

Figure 7-5. AIC Signals

## 7.2.5 Parallel I/O Signals

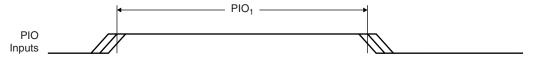

The inputs have to meet the minimum pulse width shown in Table 7-12 and represented in Figure 7-6.

Table 7-12. PIO Input Minimum Pulse Width

| Symbol           | Parameter                     | Min Pulse Width       | Units |

|------------------|-------------------------------|-----------------------|-------|

| PIO <sub>1</sub> | PIO Input Minimum Pulse Width | 3(t <sub>CP</sub> /2) | ns    |

Figure 7-6. PIO Signal

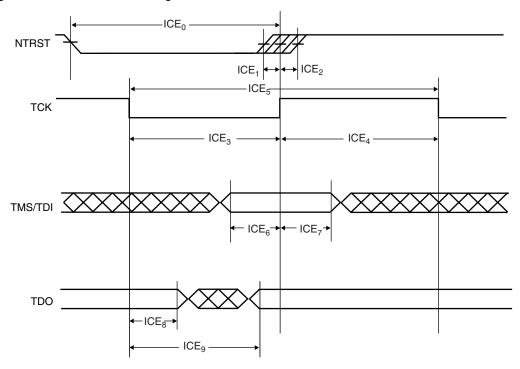

# 7.2.6 ICE Interface Signals

Table 7-13.

ICE Interface Timing Specifications

| Symbol           | Parameter                        | Conditions                | Min   | Max  | Units |

|------------------|----------------------------------|---------------------------|-------|------|-------|

| ICE <sub>0</sub> | NTRST Minimum Pulse<br>Width     |                           | 10.9  |      | ns    |

| ICE <sub>1</sub> | NTRST High Recovery to TCK High  |                           | 0.9   |      | ns    |

| ICE <sub>2</sub> | NTRST High Removal from TCK High |                           | -0.3  |      | ns    |

| ICE <sub>3</sub> | TCK Low Half-period              |                           | 23.5  |      | ns    |

| ICE <sub>4</sub> | TCK High Half-period             |                           | 22.7  |      | ns    |

| ICE <sub>5</sub> | TCK Period                       |                           | 46.1  |      | ns    |

| ICE <sub>6</sub> | TDI, TMS Setup before TCK High   |                           | 0.4   |      | ns    |

| ICE <sub>7</sub> | TDI, TMS Hold after TCK<br>High  |                           | 0.4   |      | ns    |

| ICE <sub>8</sub> | TDO Hold Time                    | C <sub>TDO</sub> = 0 pF   | 3.3   |      | ns    |

| 10E <sub>8</sub> | TDO Hold Tillle                  | C <sub>TDO</sub> derating | 0.001 |      | ns/pF |

| ICE              | TCK Low to TDO Valid             | C <sub>TDO</sub> = 0 pF   |       | 7.4  | ns    |

| ICE <sub>9</sub> | TOR LOW to TDO Valid             | C <sub>TDO</sub> derating |       | 0.28 | ns/pF |

Figure 7-7. ICE Interface Signal

# **Revision History**

| Version | page    | Comments                                                                                 |

|---------|---------|------------------------------------------------------------------------------------------|

| 1795A   |         | 10-Dec-01 First Issue                                                                    |

| 1795B   |         | 7-Aug-2002                                                                               |

|         | page 2  | Absolute Maximum Ratings: changed                                                        |

|         | page 2  | Table 1. DC Characteristics: changed                                                     |

|         | page 3  | Table 2. Power Consumption: changed                                                      |

|         | page 3  | Table 3. Power Consumption per Peripheral: changed                                       |

|         | page 9  | Table 7. Master Waveclock Parameters: changed                                            |

| 1795C   |         | 24-Mar-2004                                                                              |

|         | page 1  | Features: Change to "Fully Static Operation" values.                                     |

|         | page 9  | Figure 4. Clock Waveform: $t_R$ and $t_F$ removed, $t_{CL}$ measurement changed.         |

|         | page 13 | Table 12. Footnote 5 changed and footnote 6 added to clarify selection needs.            |

| 1795D   |         | 22-Oct-04                                                                                |

|         | page 6  | Change to Timing Results (CSR 04-320)                                                    |

|         | page 9  | Change to Table 7 and Figure 4 (CSR 04-320)                                              |

| 1795E   |         | 12-Dec-05                                                                                |

|         | all     | Reformatted in Atmel template version 5.2. Numbering properties are changed as a result. |

|         | page 9  | Table 6-1, "Master Clock Waveform Parameters," note deleted. (CSR 05-446)                |

## **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311

Fax: 1(408) 487-2600

#### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland

Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

# **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France

Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00

Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0

Fax: (49) 71-31-67-2340

1150 East Chevenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine

BP 123

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCĂTED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corporation 2005. All rights reserved. Atmel®, logo and combinations thereof, Everywhere You Are® and others, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. ARM®, the ARM Powered® logo, and others, are registered trademarks or trademarks of ARM Limited. Other terms and product names may be trademarks of others.